- 您现在的位置:买卖IC网 > PDF目录10978 > AD9837ACPZ-RL (Analog Devices Inc)IC WAVEFORM GEN PROG 10LFCSP PDF资料下载

参数资料

| 型号: | AD9837ACPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/28页 |

| 文件大小: | 0K |

| 描述: | IC WAVEFORM GEN PROG 10LFCSP |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 5,000 |

| 分辨率(位): | 10 b |

| 主 fclk: | 5MHz |

| 调节字宽(位): | 28 b |

| 电源电压: | 2.3 V ~ 5.5 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-WFDFN 裸露焊盘,CSP |

| 供应商设备封装: | 10-LFCSP-WD(3x3) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD9837

Data Sheet

Rev. A | Page 14 of 28

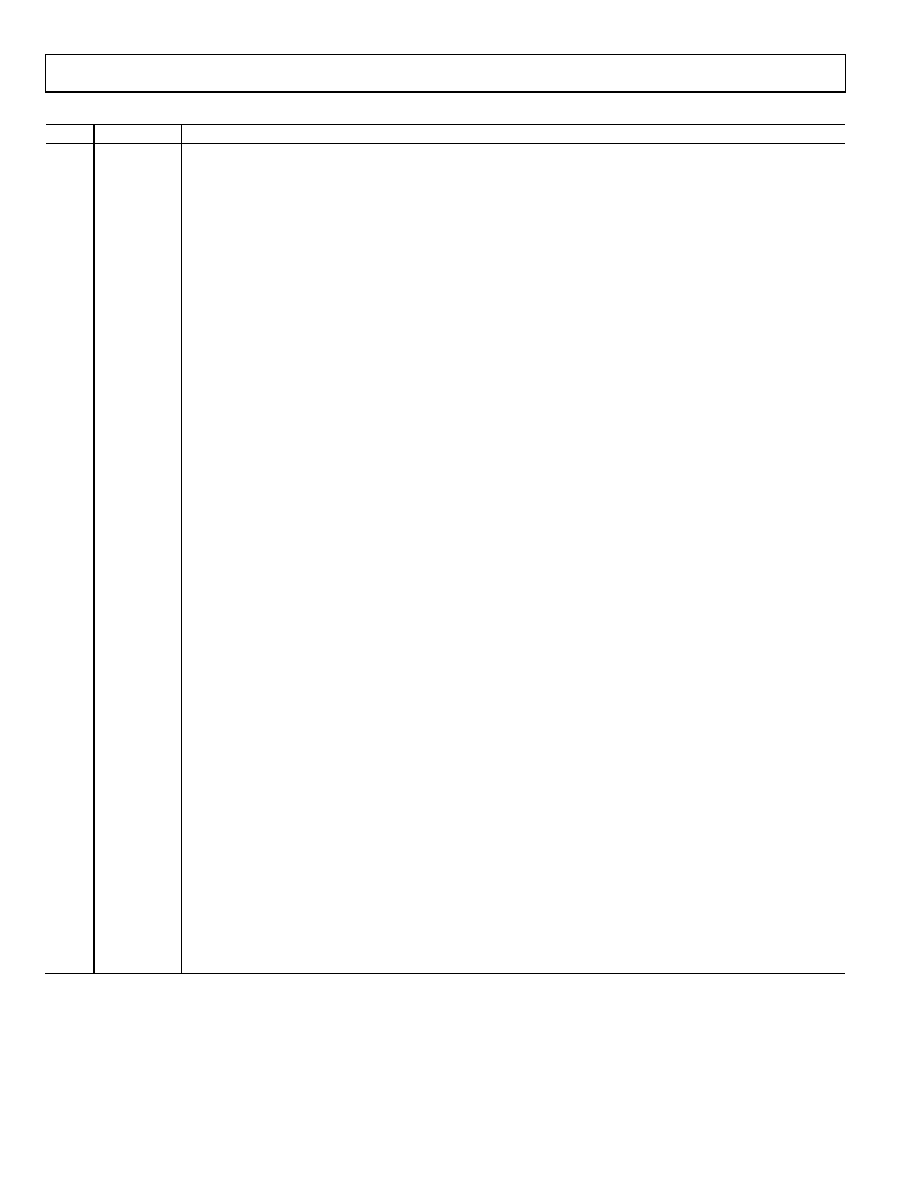

Table 7. Control Register Bit Descriptions

Bit

Bit Name

Description

D13

B28

Two write operations are required to load a complete word into either of the frequency registers.

B28 = 1 allows a complete word to be loaded into a frequency register in two consecutive writes. The first write

contains the 14 LSBs of the frequency word, and the second write contains the 14 MSBs. The first two bits of each

16-bit word define the frequency register to which the word is loaded and should, therefore, be the same for both

consecutive writes. See Table 9 for the appropriate addresses. The write to the frequency register occurs after both

words have been loaded, so the register never holds an intermediate value. An example of a complete 28-bit write

is shown in Table 10. Note, however, that consecutive 28-bit writes to the same frequency register are not allowed;

to execute consecutive 28-bit writes, you must alternate between the frequency registers.

B28 = 0 configures the 28-bit frequency register to operate as two 14-bit registers, one containing the 14 MSBs and

the other containing the 14 LSBs. In this way, the 14 MSBs of the frequency word can be altered independently of

the 14 LSBs, and vice versa. To alter the 14 MSBs or the 14 LSBs, a single write is made to the appropriate frequency

address. Bit D12 (HLB) informs the AD9837 whether the bits to be altered are the 14 MSBs or the 14 LSBs.

D12

HLB

This control bit allows the user to continuously load the MSBs or LSBs of a frequency register while ignoring the

remaining 14 bits. This is useful if the complete 28-bit resolution is not required. The HLB bit is used in conjunction

with the B28 bit (Bit D13). The HLB bit indicates whether the 14 bits to be loaded are transferred to the 14 MSBs or

the 14 LSBs of the addressed frequency register. Bit D13 (B28) must be set to 0 to change the MSBs or LSBs of a

frequency word separately. When Bit D13 (B28) is set to 1, the HLB bit is ignored.

HLB = 1 allows a write to the 14 MSBs of the addressed frequency register.

HLB = 0 allows a write to the 14 LSBs of the addressed frequency register.

D11

FSEL

The FSEL bit defines whether the FREQ0 register or the FREQ1 register is used in the phase accumulator (see Table 8).

D10

PSEL

The PSEL bit defines whether the PHASE0 register data or the PHASE1 register data is added to the output of the

phase accumulator (see Table 8).

D9

Reserved

This bit should be set to 0.

D8

RESET

This bit controls the reset function.

RESET = 1 resets internal registers to 0, which corresponds to an analog output of midscale.

RESET = 0 disables the reset function (see the Reset Function section).

D7

SLEEP1

This bit enables or disables the internal MCLK.

SLEEP1 = 1 disables the internal MCLK. The DAC output remains at its present value because the NCO is no longer

accumulating.

SLEEP1 = 0 enables the internal MCLK (see the Sleep Function section).

D6

SLEEP12

This bit powers down the on-chip DAC.

SLEEP12 = 1 powers down the on-chip DAC. This is useful when the AD9837 is used to output the MSB of the DAC data.

SLEEP12 = 0 implies that the DAC is active (see the Sleep Function section).

D5

OPBITEN

This bit, in association with the MODE bit (Bit D1), controls the output at the VOUT pin (see Table 16).

OPBITEN = 1 causes the output of the DAC to no longer be available at the VOUT pin. Instead, the MSB (or MSB/2) of

the DAC data is connected to the VOUT pin. This output is useful as a coarse clock source. The DIV2 bit (Bit D3)

controls whether the VOUT pin outputs the MSB or the MSB/2.

OPBITEN = 0 connects the output of the DAC to VOUT. The MODE bit (Bit D1) determines whether the output is

sinusoidal or triangular.

D4

Reserved

This bit must be set to 0.

D3

DIV2

DIV2 is used in association with Bit D5 (OPBITEN). See Table 16.

DIV2 = 1 causes the MSB of the DAC data to be output at the VOUT pin.

DIV2 = 0 causes the MSB/2 of the DAC data to be output at the VOUT pin.

D2

Reserved

This bit must be set to 0.

D1

MODE

This bit, in association with the OPBITEN bit (Bit D5), controls the output at the VOUT pin when the on-chip DAC is

connected to VOUT. This bit should be set to 0 if the OPBITEN bit is set to 1 (see Table 16).

MODE = 1 bypasses the SIN ROM, resulting in a triangle output from the DAC.

MODE = 0 uses the SIN ROM to convert the phase information into amplitude information, resulting in a sinusoidal

signal at the output. (The OPBITEN bit (Bit D5) must also be set to 0 for sinusoidal output.)

D0

Reserved

This bit must be set to 0.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2W3-IY-F4 | CONVERTER MOD DC/DC 24V 50W |

| VE-2W2-IY-F3 | CONVERTER MOD DC/DC 15V 50W |

| VE-2W1-IY-F2 | CONVERTER MOD DC/DC 12V 50W |

| VE-2W0-IY-F3 | CONVERTER MOD DC/DC 5V 50W |

| VE-21X-IY-F3 | CONVERTER MOD DC/DC 5.2V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9837ACPZ-RL7 | 功能描述:IC WAVEFORM GEN PROG 10LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9837BCPZ-RL | 功能描述:IC WAVEFORM GEN PROG 10LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9837BCPZ-RL7 | 功能描述:IC WAVEFORM GEN PROG 10LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9838 | 制造商:AD 制造商全称:Analog Devices 功能描述:11 mW Power, 2.3 V to 5.5 V, Complete DDS Power-down option |

| AD9838ACPZ-RL | 功能描述:IC DDS 16MHZ LOW PWR 20LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。