- 您现在的位置:买卖IC网 > PDF目录16463 > AD9854/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9854 PDF资料下载

参数资料

| 型号: | AD9854/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/52页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9854 |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 设计资源: | AD9854 Eval Brd Schematic AD9854 Eval Brd BOM |

| 标准包装: | 1 |

| 系列: | AgileRF™ |

| 主要目的: | 计时,直接数字合成(DDS) |

| 已用 IC / 零件: | AD9854 |

| 已供物品: | 板 |

| 相关产品: | AD9854ASTZ-ND - IC DDS QUADRATURE CMOS 80-LQFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9854

Rev. E | Page 23 of 52

F1

F2

0

F

RE

Q

UE

NC

Y

MODE

TW1

TW2

FSK DATA

TRIANGLE

BIT

010 (RAMPED FSK)

F1

F2

I/O UD CLK

006

36

-04

0

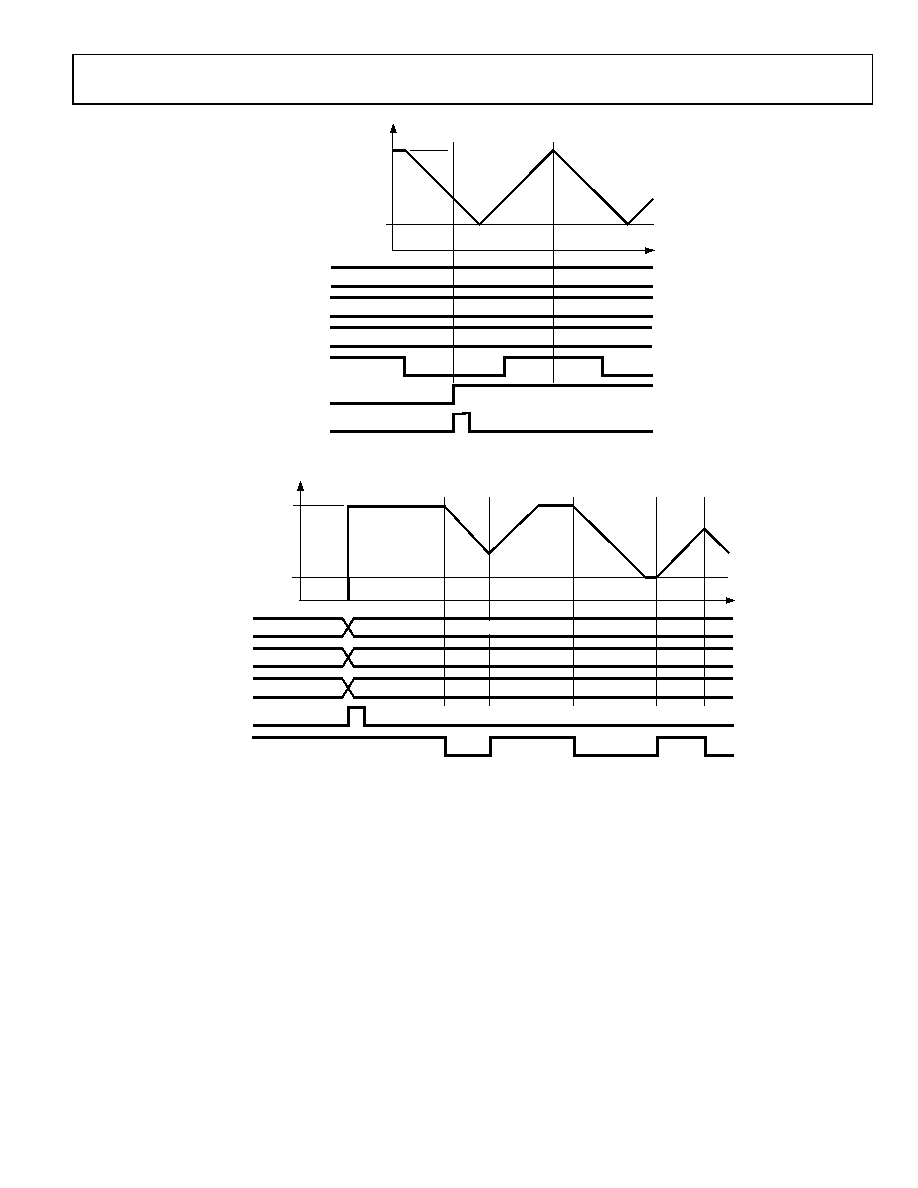

Figure 40. Effect of Triangle Bit in Ramped FSK Mode

F1

F2

0

F

RE

Q

UE

NC

Y

MODE

TW1

TW2

FSK DATA

F1

F2

000 (DEFAULT)

0

010 (RAMPED FSK)

I/O UD CLK

00

63

6-

0

41

Figure 41. Effect of Premature Ramped FSK Data

Figure 41 shows that premature toggling causes the ramp to

immediately reverse itself and proceed at the same rate and

resolution until the original frequency is reached.

The control register contains a triangle bit at Parallel Register

Address 1F hex. Setting this bit high in Mode 010 causes an

automatic ramp-up and ramp-down between F1 and F2 to

occur without toggling Pin 29, as shown in Figure 40. The logic

state of Pin 29 has no effect once the triangle bit is set high. This

function uses the ramp rate clock time period and the step size

of the delta frequency word to form a continuously sweeping

linear ramp from F1 to F2 and back to F1 with equal dwell

times at every frequency. Use this function to automatically

sweep between any two frequencies from dc to Nyquist.

In the ramped FSK mode with the triangle bit set high, an

automatic frequency sweep begins at either F1 or F2, according

to the logic level on Pin 29 (FSK input pin) when the triangle

bit’s rising edge occurs (Figure 42). If the FSK data bit is high

instead of low, F2, rather than F1, is chosen as the start frequency.

Additional flexibility in the ramped FSK mode is provided by

the AD9854’s ability to respond to changes in the 48-bit delta

frequency word and/or the 20-bit ramp rate counter at any time

during the ramping from F1 to F2 or vice versa. To create these

nonlinear frequency changes, it is necessary to combine several

linear ramps with different slopes in a piecewise fashion. This is

done by programming and executing a linear ramp at a rate or

slope and then altering the slope (by changing the ramp rate

clock or delta frequency word, or both). Changes in slope can

be made as often as needed before the destination frequency has

been reached to form the desired nonlinear frequency sweep

response. These piecewise changes can be precisely timed using

相关PDF资料 |

PDF描述 |

|---|---|

| LK2125R22K-T | INDUCTOR MULTILAYER .22UH 0805 |

| 6588719-2 | C/A MTRJ-LC DUP OFNR XG |

| M3UUK-2006R | IDC CABLE - MKS20K/MC20M/MKS20K |

| EEM30DTMI-S189 | CONN EDGECARD 60POS R/A .156 SLD |

| 6278033-3 | C/A MT-RJ/MT-RJ SM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9856 | 制造商:AD 制造商全称:Analog Devices 功能描述:CMOS 200 MHz Quadrature Digital Upconverter |

| AD9856/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For Digital Up Converter 56 Pin LFCSP Ep 制造商:Analog Devices 功能描述:DGTL UP CNVRTR 56LFCSP - Bulk |

| AD9856AST | 制造商:Analog Devices 功能描述:Digital Up Converter 48-Pin LQFP Tray 制造商:Analog Devices 功能描述:IC MODULATOR DIGITAL |

| AD9856ASTZ | 功能描述:IC UPCONVERTER DGTL QUAD 48TQFP RoHS:是 类别:RF/IF 和 RFID >> RF 其它 IC 和模块 系列:AD9856 标准包装:100 系列:* |

| AD9857 | 制造商:AD 制造商全称:Analog Devices 功能描述:CMOS 200 MSPS 14-Bit Quadrature Digital Upconverter |

发布紧急采购,3分钟左右您将得到回复。