参数资料

| 型号: | ADN2807ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/20页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 48LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH,STM |

| 输入: | CML |

| 输出: | CML |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 622MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP |

| 包装: | 托盘 |

ADN2807

Rev. A | Page 4 of 20

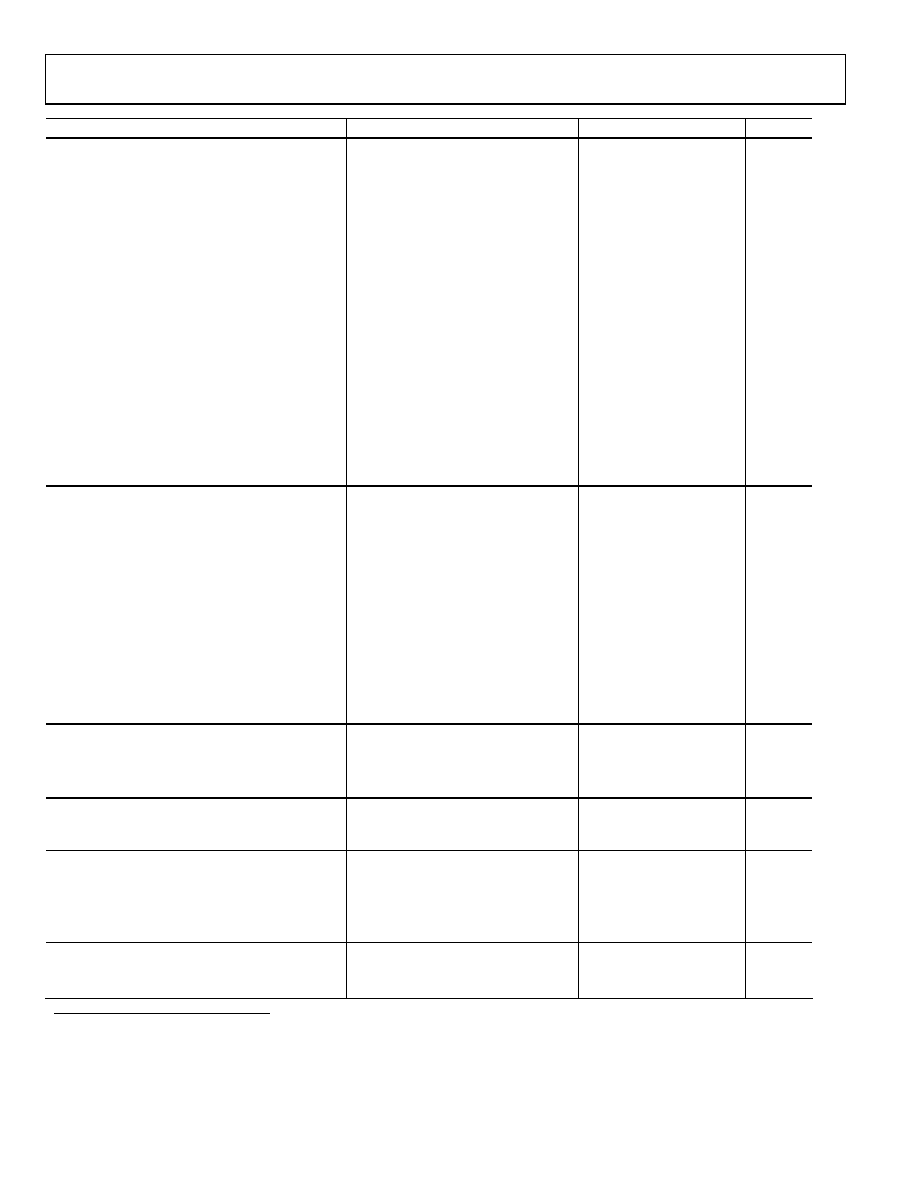

Parameter

Conditions

Min

Typ

Max

Unit

PHASE-LOCKED LOOP CHARACTERISTICS

PIN–NIN = 10 mV p-p

Jitter Transfer BW

OC-12

140

200

kHz

OC-3

48

85

kHz

Jitter Peaking

OC-12

0.004

dB

OC-3

0.002

dB

Jitter Generation

OC-12, 12 kHz to 5 MHz

0.003

UI rms

0.02

0.04

UI p-p

OC-3, 12 kHz to 1.3 MHz

0.002

UI rms

0.02

0.04

UI p-p

Jitter Tolerance

OC-12

30 Hz3

100

UI p-p

300 Hz

44

UI p-p

25 kHz

5.8

UI p-p

250 kHz3

1.0

UI p-p

OC-3

30 Hz3

50

UI p-p

300 Hz3

23.5

UI p-p

6500 Hz

6.0

UI p-p

65 kHz3

1.0

UI p-p

CML OUTPUTS (CLKOUTP/N, DATAOUTP/N)

Single-Ended Output Swing

400

488

540

mV

Differential Output Swing

850

975

1100

mV

Output High Voltage

VOH

VCC

V

Output Low Voltage

VOL, referred to VCC

–0.60

–0.30

V

Rise Time

20% to 80%

150

ps

Fall Time

80% to 20%

150

ps

Setup Time

OC-12

750

ps

OC-3

3145

ps

Hold Time

OC-12

750

ps

OC-3

3150

ps

REFCLK DC INPUT CHARACTERISTICS

Input Voltage Range

@ REFCLKP or REFCLKN

0

VCC

V

Peak-to-Peak Differential Input

100

mV

Common-Mode Level

DC-coupled, single-ended

VCC/2

V

TEST DATA DC INPUT CHARACTERISTICS4

(TDINP/N)

CML inputs

Peak-to-Peak Differential Input Voltage

0.8

V

LVTTL DC INPUT CHARACTERISTICS

Input High Voltage

VIH

2.0

V

Input Low Voltage

VIL

0.8

V

Input Current

VIN = 0.4 V or VIN = 2.4 V

–5

+5

A

Input Current (SEL0 and SEL1 Only)5

VIN = 0.4 V or VIN = 2.4 V

–5

+50

A

LVTTL DC OUTPUT CHARACTERISTICS

Output High Voltage

VOH, IOH = –2.0 mA

2.4

V

Output Low Voltage

VOL, IOL = +2.0 mA

0.4

V

1PIN and NIN should be driven differentially, ac-coupled for optimum sensitivity.

2PWD measurement made on quantizer outputs in BYPASS mode.

3Jitter tolerance measurements are equipment limited.

4TDINP/N are CML inputs. If the drivers to the TDINP/N inputs are anything other than CML, they must be ac-coupled.

5SEL0 and SEL1 have internal pull-down resistors, causing higher IIH.

相关PDF资料 |

PDF描述 |

|---|---|

| ADN2811ACPZ-CML | IC CLK/DATA REC W/AMP 48-LFCSP |

| ADN2812ACPZ-RL7 | IC CLOCK/DATA RECOVERY 32LFCSP |

| ADN2813ACPZ-500RL7 | IC CLK/DATA REC 1.25GBPS 32LFCSP |

| ADN2814ACPZ-500RL7 | IC CLK/DATA REC 675MBPS 32-LFCSP |

| ADN2815ACPZ | IC CLK/DATA REC 1.25GBPS 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2807ACPZ-RL | 功能描述:IC CLOCK/DATA RECOVERY 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2809 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multi-Rate to 2.7Gbps Clock and Data Recovery IC with Limiting Amplifier |

| ADN2809XCP | 制造商:AD 制造商全称:Analog Devices 功能描述:Multi-Rate to 2.7Gbps Clock and Data Recovery IC with Limiting Amplifier |

| ADN2809XCP-RL | 制造商:AD 制造商全称:Analog Devices 功能描述:Multi-Rate to 2.7Gbps Clock and Data Recovery IC with Limiting Amplifier |

| ADN2811 | 制造商:AD 制造商全称:Analog Devices 功能描述:OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

发布紧急采购,3分钟左右您将得到回复。