参数资料

| 型号: | ADN2814ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/28页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 675MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

ADN2814

Rev. C | Page 23 of 28

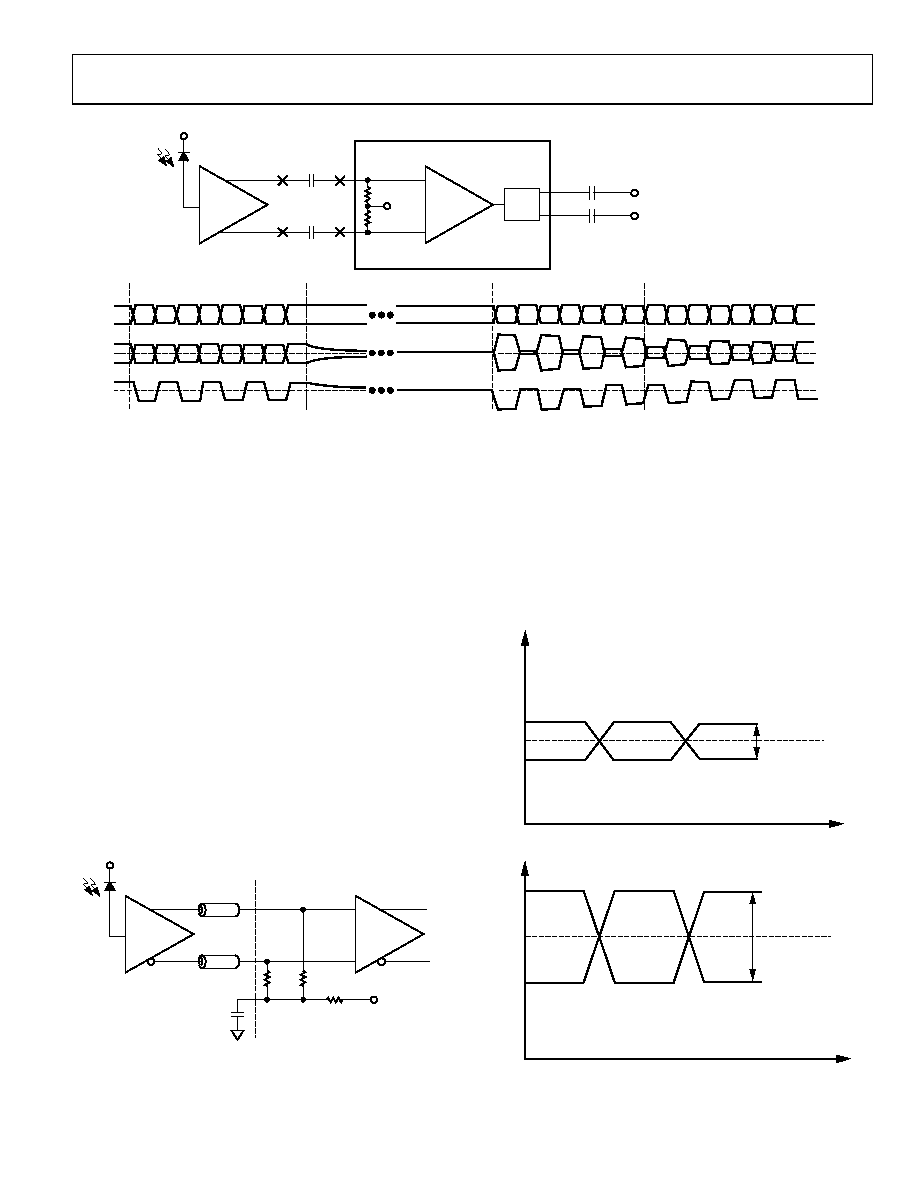

50

Ω

50

Ω

PIN

VREF

NIN

CIN

COUT

V1

CIN

V1b

V2

V2b

TIA

LIMAMP

CDR

+

–

VCC

DATAOUTP

DATAOUTN

1

V1

V1b

V2

V2b

VDIFF

23

4

VREF

VTH

ADN2814

VDIFF = V2–V2b

VTH = ADN2813 QUANTIZER THRESHOLD

NOTES:

1. DURING DATA PATTERNS WITH HIGH TRANSITION DENSITY, DIFFERENTIAL DC VOLTAGE AT V1 AND V2 IS ZERO.

2. WHEN THE OUTPUT OF THE TIA GOES TO CID, V1 AND V1b ARE DRIVEN TO DIFFERENT DC LEVELS. V2 AND V2b DISCHARGE TO THE

VREF LEVEL, WHICH EFFECTIVELY INTRODUCES A DIFFERENTIAL DC OFFSET ACROSS THE AC COUPLING CAPACITORS.

3. WHEN THE BURST OF DATA STARTS AGAIN, THE DIFFERENTIAL DC OFFSET ACROSS THE AC COUPLING CAPACITORS IS APPLIED TO

THE INPUT LEVELS CAUSING A DC SHIFT IN THE DIFFERENTIAL INPUT. THIS SHIFT IS LARGE ENOUGH SUCH THAT ONE OF THE STATES,

EITHER HIGH OR LOW DEPENDING ON THE LEVELS OF V1 AND V1b WHEN THE TIA WENT TO CID, IS CANCELED OUT. THE QUANTIZER

DOES NOT RECOGNIZE THIS AS A VALID STATE.

4. THE DC OFFSET SLOWLY DISCHARGES UNTIL THE DIFFERENTIAL INPUT VOLTAGE EXCEEDS THE SENSITIVITY OF THE ADN2814. THE

QUANTIZER CAN RECOGNIZE BOTH HIGH AND LOW STATES AT THIS POINT.

04949-

027

Figure 26. Example of Baseline Wander

DC-COUPLED APPLICATION

The inputs to the ADN2814 can also be dc-coupled. This may

be necessary in burst mode applications, where there are long

periods of CIDs, and baseline wander cannot be tolerated. If the

inputs to the ADN2814 are dc-coupled, care must be taken not

to violate the input range and common-mode level require-

coupling is required, and the output levels of the TIA do not

adhere to the levels shown in Figure 28, then level shifting

and/or an attenuator must be between the TIA outputs and the

ADN2814 inputs.

50

Ω

0.1

μF

50

Ω

3k

Ω

NIN

PIN

ADN2814

2.5V

VREF

50

Ω

50

Ω

TIA

VCC

04949-

028

Figure 27. DC-Coupled Application

PIN

IN

PU

T

(V)

V p-p = PIN – NIN = 2

× VSE = 10mV AT SENSITIVITY

VSE = 5mV MIN

VCM = 2.3V MIN

(DC-COUPLED)

NIN

04949-029

Figure 28. Minimum Allowed DC-Coupled Input Levels

PIN

INPUT

(V)

V p-p = PIN – NIN = 2

× VSE = 2.0V MAX

VSE = 1.0V MAX

VCM = 2.3V

(DC-COUPLED)

NIN

04949-

030

Figure 29. Maximum Allowed DC-Coupled Input Levels

相关PDF资料 |

PDF描述 |

|---|---|

| SM802105UMG | IC SYNTHESIZER 2CH 24-QFN |

| SM802104UMG | IC SYNTHESIZER 2CH 24-QFN |

| SM843001-212KA | IC CLK SYNTHESIZER FIBRE 8-TSSOP |

| MS27466T25F4S | CONN RCPT 56POS WALL MT W/SCKT |

| ADN2805ACPZ | IC CLK/DATA REC 1.25GBPS 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2814ACPZ-500RL7 | 功能描述:IC CLK/DATA REC 675MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2814ACPZ-RL7 | 功能描述:IC CLK/DATA REC 675MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2814XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Continuous Rate 12.3 Mb/s to 675 Mb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2815 | 制造商:AD 制造商全称:Analog Devices 功能描述:Continuous Rate 10 Mb/s to 1.25 Gb/s Clock and Data Recovery IC |

| ADN2815ACPZ | 功能描述:IC CLK/DATA REC 1.25GBPS 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。