参数资料

| 型号: | ADN2814ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/28页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 675MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页

ADN2814

Data Sheet

Rev. C | Page 8 of 28

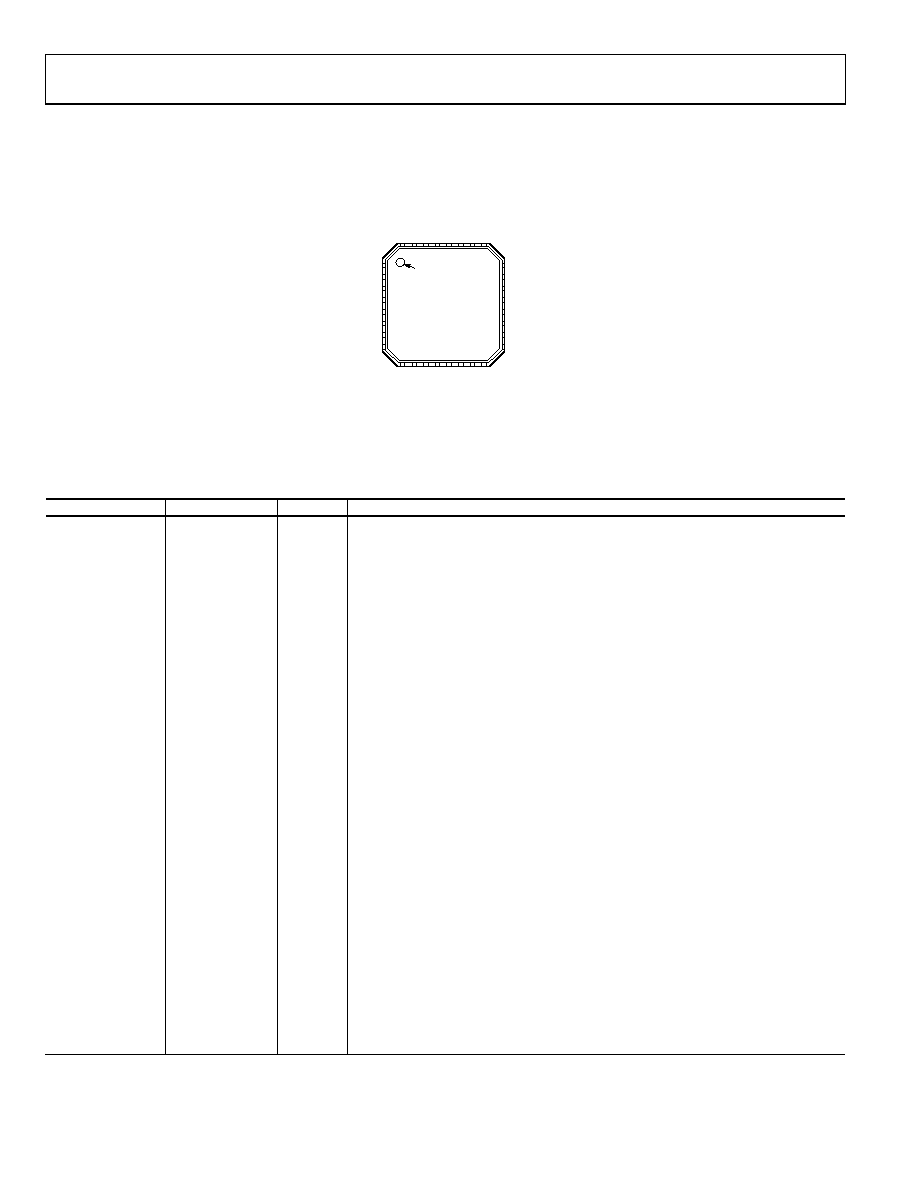

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VCC 1

VCC 2

VREF 3

PIN 1

INDIC ATOR

TOP VIEW

(Not to Scale)

24 VCC

23 VEE

22 LOS

21 SDA

32

V

C

20 SCK

19 SADDR5

18 VCC

17 VEE

T

HRA

DJ

9

R

E

FC

LK

P

1

0

RE

F

CL

KN

11

VC

C

1

2

VE

E

1

3

CF

214

CF

115

LO

L

1

6

NIN 4

PIN 5

SLICEP 6

SLICEN 7

VEE 8

31

V

C

30

V

E

29

D

A

TA

O

U

T

P

28

D

A

TA

O

U

T

N

27

S

Q

UE

L

C

H

26

CL

KO

UT

P

25

CL

KO

UT

N

ADN2814*

* THERE IS AN EXPOSED PAD ON THE BOTTOM OF

THE PACKAGE THAT MUST BE CONNECTED TO GND.

0

49

-00

4

Figure 5. Pin Configuration

Table 5. Pin Function Descriptions

Pin No.

Mnemonic

Type1

Description

1

VCC

AI

Connect to VCC.

2

VCC

P

Power for Limiting Amplifier, LOS.

3

VREF

AO

Internal VREF Voltage. Decouple to GND with a 0.1 μF capacitor.

4

NIN

AI

Differential Data Input. CML.

5

PIN

AI

Differential Data Input. CML.

6

SLICEP

AI

Differential Slice Level Adjust Input.

7

SLICEN

AI

Differential Slice Level Adjust Input.

8

VEE

P

GND for Limiting Amplifier, LOS.

9

THRADJ

AI

LOS Threshold Setting Resistor.

10

REFCLKP

DI

Differential REFCLK Input. 10 MHz to 160 MHz.

11

REFCLKN

DI

Differential REFCLK Input. 10 MHz to 160 MHz.

12

VCC

P

VCO Power.

13

VEE

P

VCO GND.

14

CF2

AO

Frequency Loop Capacitor.

15

CF1

AO

Frequency Loop Capacitor.

16

LOL

DO

Loss-of-Lock Indicator. LVTTL active high.

17

VEE

P

FLL Detector GND.

18

VCC

P

FLL Detector Power.

19

SADDR5

DI

Slave Address Bit 5.

20

SCK

DI

I2C Clock Input.

21

SDA

DI

I2C Data Input.

22

LOS

DO

Loss-of-Signal Detect Output. Active high. LVTTL.

23

VEE

P

Output Buffer, I2C GND.

24

VCC

P

Output Buffer, I2C Power.

25

CLKOUTN

DO

Differential Recovered Clock Output. LVDS.

26

CLKOUTP

DO

Differential Recovered Clock Output. LVDS.

27

SQUELCH

DI

Disable Clock and Data Outputs. Active high. LVTTL.

28

DATAOUTN

DO

Differential Recovered Data Output. LVDS.

29

DATAOUTP

DO

Differential Recovered Data Output. LVDS.

30

VEE

P

Phase Detector, Phase Shifter GND.

31

VCC

P

Phase Detector, Phase Shifter Power.

32

VCC

AI

Connect to VCC.

Exposed Pad

Pad

P

Connect to GND.

Works as a heat sink.

1 Type: P = power, AI = analog input, AO = analog output, DI = digital input, DO = digital output.

相关PDF资料 |

PDF描述 |

|---|---|

| SM802105UMG | IC SYNTHESIZER 2CH 24-QFN |

| SM802104UMG | IC SYNTHESIZER 2CH 24-QFN |

| SM843001-212KA | IC CLK SYNTHESIZER FIBRE 8-TSSOP |

| MS27466T25F4S | CONN RCPT 56POS WALL MT W/SCKT |

| ADN2805ACPZ | IC CLK/DATA REC 1.25GBPS 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2814ACPZ-500RL7 | 功能描述:IC CLK/DATA REC 675MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2814ACPZ-RL7 | 功能描述:IC CLK/DATA REC 675MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2814XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Continuous Rate 12.3 Mb/s to 675 Mb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2815 | 制造商:AD 制造商全称:Analog Devices 功能描述:Continuous Rate 10 Mb/s to 1.25 Gb/s Clock and Data Recovery IC |

| ADN2815ACPZ | 功能描述:IC CLK/DATA REC 1.25GBPS 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。