参数资料

| 型号: | ADS1259BIPWR |

| 厂商: | Texas Instruments |

| 文件页数: | 10/48页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT SPI 14KSPS 20TSSOP |

| 标准包装: | 2,000 |

| 位数: | 24 |

| 采样率(每秒): | 14k |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个单端,单极;2 个单端,双极;1 个差分,单极;1 个差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

H

=

H

(f)

H

(f)

=

(f)

sinc

5

N

5

sin

512

f

p

f

CLK

64

sin

8

f

p

f

CLK

sin

512

R

f

p

f

CLK

R

sin

512

f

p

f

CLK

N

Analog

Modulator

sinc

5

Filter

(decimateby64)

sinc Filter

1

f

/512

CLK

ModulatorRate=f

/8

CLK

sinc Filter

2

DR[2:0]RegisterBits

(ProgramDecimation)

Output

DataRate=f

/(R

)

CLK

512

SINC2RegisterBit

(0=sinc )

1

SBAS424D

– JUNE 2009 – REVISED AUGUST 2011

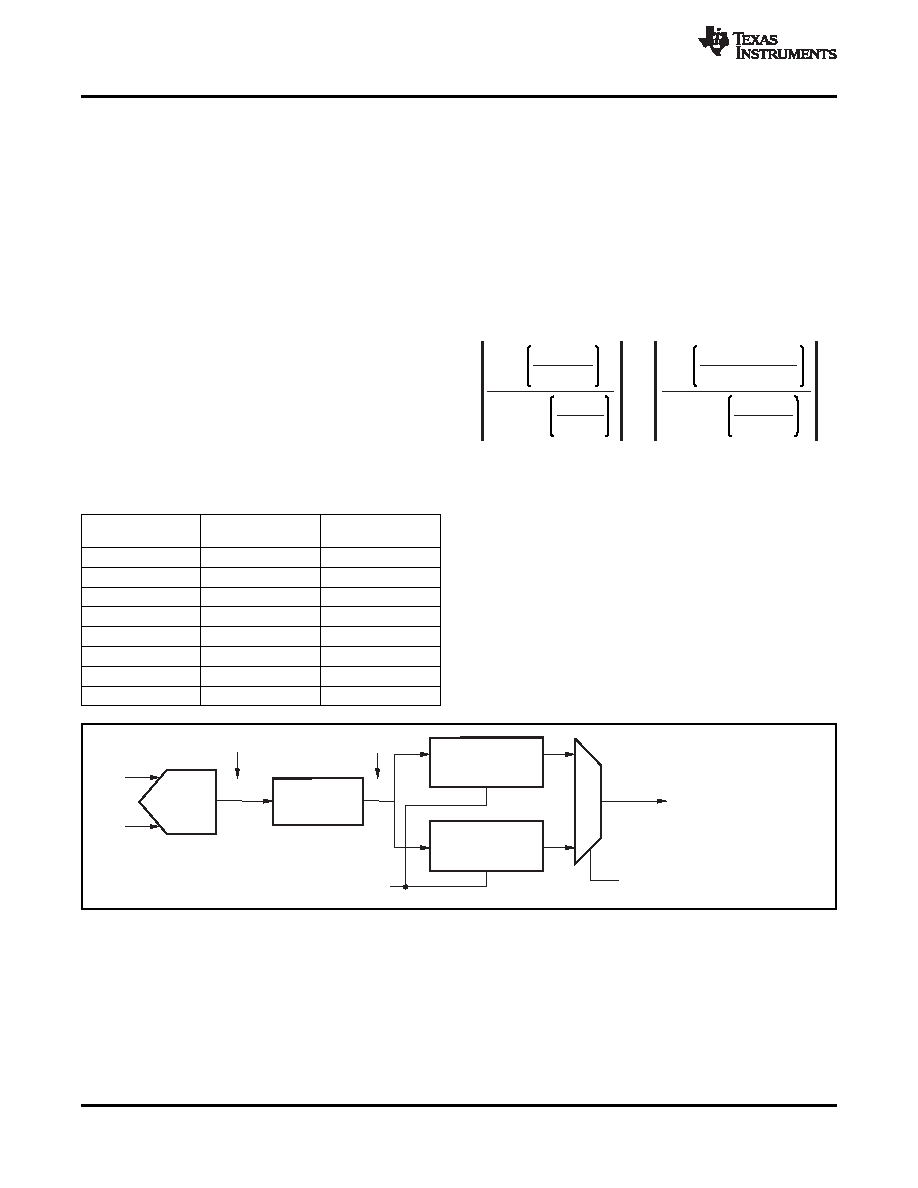

DIGITAL FILTER

The SINC2 register bit selects either the sinc1 or sinc2

filter. The sinc1 filter settles in one conversion cycle

The programmable low-pass digital filter receives the

while the sinc2 filter settles in two conversion cycles.

modulator output and produces a high-resolution

However, the sinc2 filter has the benefit of wider

digital output. By adjusting the amount of filtering,

frequency notches which improve line cycle rejection.

tradeoffs can be made between resolution and data

rate: filter more for higher resolution, filter less for

FREQUENCY RESPONSE

higher data rate.

The low-pass digital filter sets the overall frequency

The filter consists of two sections: a fixed decimation

response of the ADS1259. The filter response is the

sinc5 filter followed by a variable decimation filter,

product of the fixed and programmable filter sections,

configurable as sinc1 or sinc2, as illustrated in

and is given by Equation 5:

and reduces the data rate of the modulator from

fCLK/8 to fCLK/512. The second filter stage receives the

data from the sinc5 filter. The second filter stage has

programmable averaging (or decimation) and can be

configured in either sinc1 or sinc2 mode. The

decimation ratio of this stage sets the final output

data rate. As detailed in Table 3, the DR[2:0] register

bits program the decimation ratio and the final output

data rate. The output data rates are identical for both

where:

sinc1 and sinc2 filters.

N = 1 (sinc1)

Table 3. Decimation Ratio of Final Filter Stage

N = 2 (sinc2)

R = Decimation ratio (refer to Table 3)

(5)

DR[2:0] REGISTER

DECIMATION

BITS

RATIO (R)

DATA RATE (SPS)

The digital filter attenuates noise on the modulator

111

1

14400

output, including noise from within the ADS1259 and

110

4

3600

external noise present within the ADS1259 input

101

12

1200

signal.

Adjusting

the

filtering

by

changing

the

decimation ratio used in the programmable filter

100

36

400

changes the filter bandwidth. With a higher number of

011

240

60

decimation, the bandwidth is reduced and more noise

010

288

50

is attenuated.

001

864

16.6

000

1440

10

Figure 39. Block Diagram of Digital Filter

18

Copyright

2009–2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| ADS1286UB/2K5G4 | IC ADC 12BIT SPI 37KSPS 8SOIC |

| ADS1601IPFBTG4 | IC ADC 16BIT 1.25MSPS 48-TQFP |

| ADS62C17IRGC25 | IC ADC 11BIT 200MSPS DUAL 64VQFN |

| ADS62P45IRGC25 | IC ADC 14B SER/PAR 125M 64VQFN |

| ADS7812U/1KE4 | IC 12BIT 35MW SER OUT ADC 16SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS1259EVM | 功能描述:数据转换 IC 开发工具 ADS1259 Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| ADS1259EVM | 制造商:Texas Instruments 功能描述:DEVELOPMENT TOOL |

| ADS1259EVM-PDK | 功能描述:数据转换 IC 开发工具 ADS1259 Perf Demo Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| ADS1259EVM-PDK | 制造商:Texas Instruments 功能描述:DEVELOPMENT TOOL |

| ADS1259IPW | 功能描述:模数转换器 - ADC Low-Noise 14kSPS 24B ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。