- 您现在的位置:买卖IC网 > PDF目录15527 > ADSP-3PARCBF548E02 (Analog Devices Inc)KIT DEV STARTER BF548 PDF资料下载

参数资料

| 型号: | ADSP-3PARCBF548E02 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/100页 |

| 文件大小: | 0K |

| 描述: | KIT DEV STARTER BF548 |

| 产品培训模块: | Arcturus uCBF54x-EMM |

| 特色产品: | uCBF54x Start Kit and System Module by Arcturus |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | DSP |

| 适用于相关产品: | ADSP-BF548 |

| 所含物品: | 板,线缆,CD,带麦克风的耳机,模块,电源 |

| 相关产品: | ADSP-BF548MBBCZ-5M-ND - IC DSP 533MHZ W/DDR 400CSPBGA ADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

Rev. C

|

Page 17 of 100

|

February 2010

Sleep Operating Mode—High Dynamic Power Savings

The sleep mode reduces dynamic power dissipation by disabling

the clock to the processor core (CCLK). The PLL and system

clock (SCLK), however, continue to operate in this mode. Typi-

cally an external event or RTC activity will wake up the

processor. In the sleep mode, assertion of a wakeup event

enabled in the SIC_IWRx register causes the processor to sense

the value of the BYPASS bit in the PLL control register

(PLL_CTL). If BYPASS is disabled, the processor transitions to

the full on mode. If BYPASS is enabled, the processor transi-

tions to the active mode.

In the sleep mode, system DMA access to L1 memory is not

supported.

Deep Sleep Operating Mode—Maximum Dynamic Power

Savings

The deep sleep mode maximizes dynamic power savings by dis-

abling the clocks to the processor core (CCLK) and to all

synchronous peripherals (SCLK). Asynchronous peripherals,

such as the RTC, may still be running but will not be able to

access internal resources or external memory. This

powered-down mode can only be exited by assertion of the reset

interrupt (RESET) or by an asynchronous interrupt generated

by the RTC. In deep sleep mode, an asynchronous RTC inter-

rupt causes the processor to transition to the active mode.

Assertion of RESET while in deep sleep mode causes the proces-

sor to transition to the full on mode.

Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling

the voltage and clocks to the processor core (CCLK) and to all

the synchronous peripherals (SCLK). The internal voltage regu-

lator for the processor can be shut off by using the

bfrom_SysControl() function in the on-chip ROM. This sets the

internal power supply voltage (VDDINT) to 0 V to provide the

greatest power savings mode. Any critical information stored

internally (memory contents, register contents, and so on) must

be written to a non-volatile storage device prior to removing

power if the processor state is to be preserved.

Since VDDEXT is still supplied in this mode, all of the external

pins three-state, unless otherwise specified. This allows other

devices that may be connected to the processor to have power

still applied without drawing unwanted current.

The internal supply regulator can be woken up by CAN, by the

MXVR, by the keypad, by the up/down counter, by the USB,

and by some GPIO pins. It can also be woken up by a real-time

clock wakeup event or by asserting the RESET pin. Waking up

from hibernate state initiates the hardware reset sequence.

With the exception of the VR_CTL and the RTC registers, all

internal registers and memories lose their content in hibernate

state. State variables may be held in external SRAM or DDR

memory.

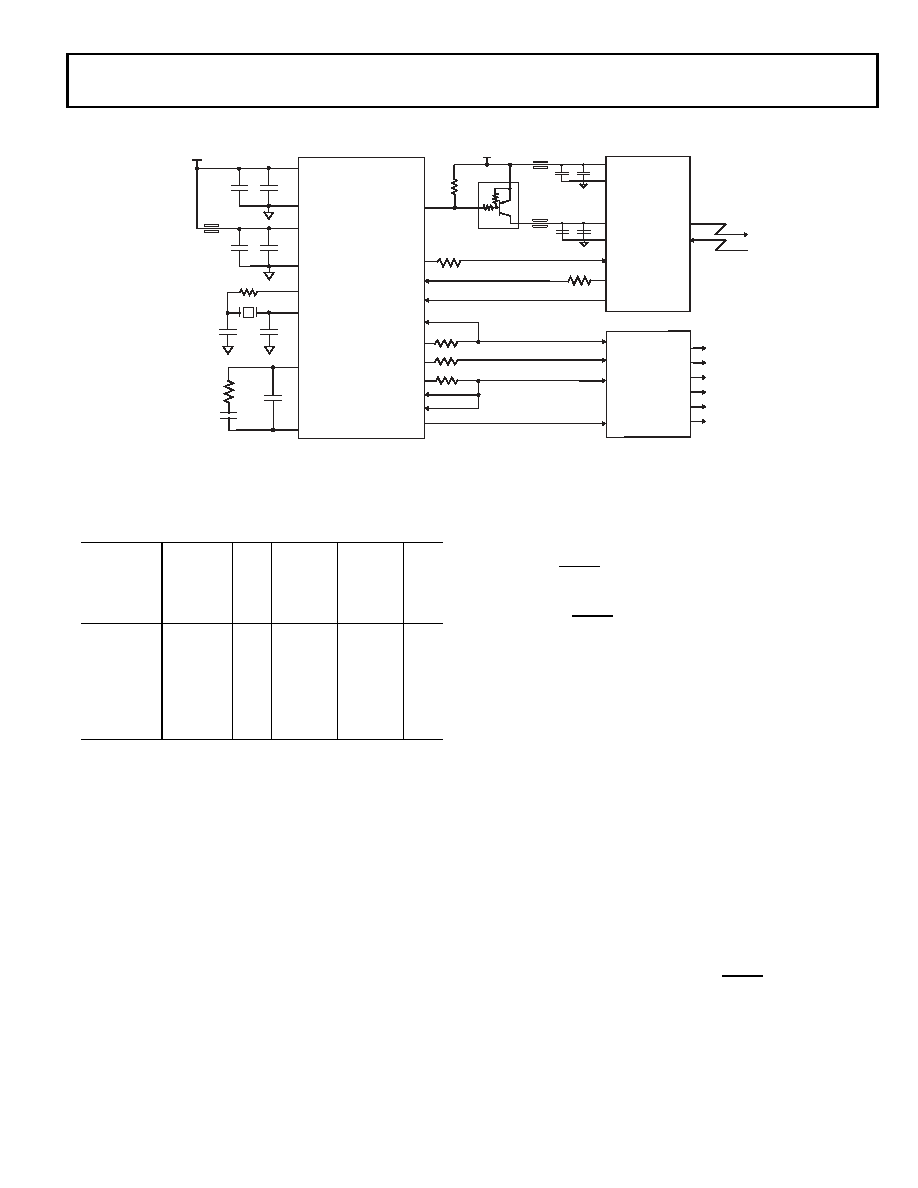

Figure 5. MXVR MOST Connection

600Z

MLF_M

MOST

NETWORK

AUDIO

CHANNELS

GNDMP

VDDMP

MOST FOT

TXVCC

TX_DATA

RX_DATA

STATUS

AUDIO DAC

27

R1

330

C1

0.047 F

0.1 F

0.01 F

C2

330pF

ADSP-BF549

MXI

MXO

MLF_P

PG11/

MTXON

PH5/MTX

PH6/MRX

PH7/

MRXON

PC1/MMCLK

MFS

PC5/MBCLK

PC3/TSCLK0

PC7/RSCLK0

PC4/RFS0

PC2/DT0PRI

SDATA

L/RCLK

BCLK

MCLK

33

1.25V

GND

VDDINT

1%

2% PPS

0

TXGND

5.0V

RXVCC

RXGND

600Z

10k

24.576MHz

XN4114

Table 5. Power Settings

M

o

de/

State

PLL

By

p

a

ss

e

d

Co

re

Cl

o

ck

(CC

L

K

)

Sys

te

m

Cl

o

ck

(S

CLK)

Co

re

Po

w

e

r

Full On

Enabled

No

Enabled

On

Active

Enabled/

Disabled

Yes

Enabled

On

Sleep

Enabled

-

Disabled

Enabled

On

Deep Sleep

Disabled

-

Disabled

On

Hibernate

Disabled

-

Disabled

Off

相关PDF资料 |

PDF描述 |

|---|---|

| ECM25DCTI-S288 | CONN EDGECARD 50POS .156 EXTEND |

| GCM18DTKI-S288 | CONN EDGECARD 36POS .156 EXTEND |

| UCC3957MTR-2 | IC LI-ION PROTECT CIRCUIT 16QSOP |

| GBM28DRMI-S288 | CONN EDGECARD 56POS .156 EXTEND |

| UCC3957MTR-1G4 | IC LI-ION PROTECT CIRCUIT 16QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-3PARCBF548M01 | 功能描述:MODULE BOARD BF548 RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器或微处理器模块 系列:Blackfin® 产品目录绘图:DLP-245SY-G 标准包装:1 系列:USB 模块/板类型:开发板 适用于相关产品:USB 其它名称:813-1006 |

| ADSP-BF504BCPZ-3F | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF504BCPZ-4 | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF504BCPZ-4F | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF504KCPZ-3F | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。