- 您现在的位置:买卖IC网 > PDF目录19403 > ADSP-BF531SBBCZ4RL (Analog Devices Inc)IC DSP CTLR 16BIT 400MHZ 160-CSP PDF资料下载

参数资料

| 型号: | ADSP-BF531SBBCZ4RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 400MHZ 160-CSP |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | SPI,SSP,UART |

| 时钟速率: | 400MHz |

| 非易失内存: | ROM(1 kB) |

| 芯片上RAM: | 52kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-LFBGA,CSPBGA |

| 供应商设备封装: | 160-CSPBGA(12x12) |

| 包装: | 标准包装 |

| 其它名称: | ADSP-BF531SBBCZ4RLDKR |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�ADSP-BF531� /� ADSP-BF532� /� ADSP-BF533�

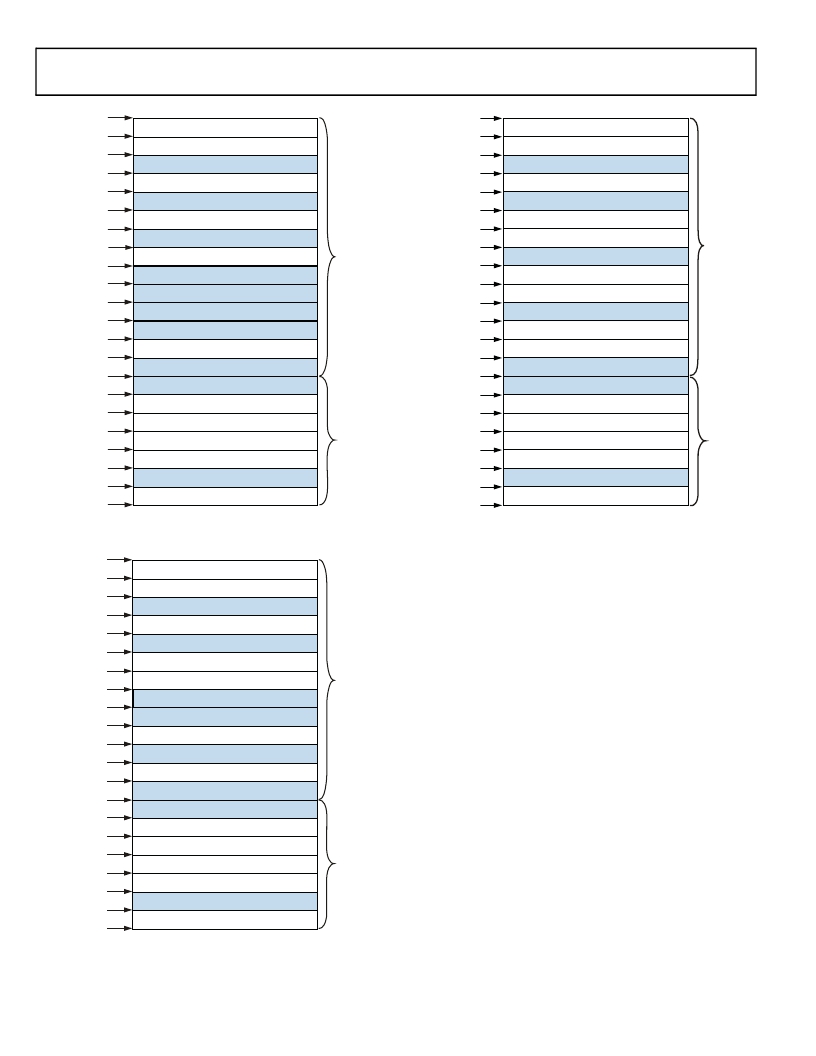

�0xFFFF� FFFF�

�CORE� MMR� REGISTERS� (2M� BYTE)�

�0xFFE0� 0000�

�SYSTEM� MMR� REGISTERS� (2M� BYTE)�

�0xFFC0� 0000�

�RESERVED�

�0xFFB0� 1000�

�SCRATCHPAD� SRAM� (4K� BYTE)�

�0xFFB0� 0000�

�RESERVED�

�0xFFA1� 4000�

�INSTRUCTION� SRAM/CACHE� (16K� BYTE)�

�0xFFA1� 0000�

�RESERVED�

�0xFFA0� C000�

�INSTRUCTION� SRAM� (16K� BYTE)�

�0xFFA0� 8000�

�RESERVED�

�0xFFA0� 0000�

�RESERVED�

�0xFF90� 8000�

�RESERVED�

�0xFF90� 4000�

�RESERVED�

�0xFF80� 8000�

�DATA� BANK� A� SRAM/CACHE� (16K� BYTE)�

�0xFF80� 4000�

�RESERVED�

�0xEF00� 0000�

�RESERVED�

�0x2040� 0000�

�ASYNC� MEMORY� BANK� 3� (1M� BYTE)�

�0x2030� 0000�

�ASYNC� MEMORY� BANK� 2� (1M� BYTE)�

�0x2020� 0000�

�ASYNC� MEMORY� BANK� 1� (1M� BYTE)�

�0x2010� 0000�

�ASYNC� MEMORY� BANK� 0� (1M� BYTE)�

�0x2000� 0000�

�RESERVED�

�0x0800� 0000�

�SDRAM� MEMORY� (16M� BYTE� TO� 128M� BYTE)�

�0x0000� 0000�

�Figure� 3.� ADSP-BF531� Internal/External� Memory� Map�

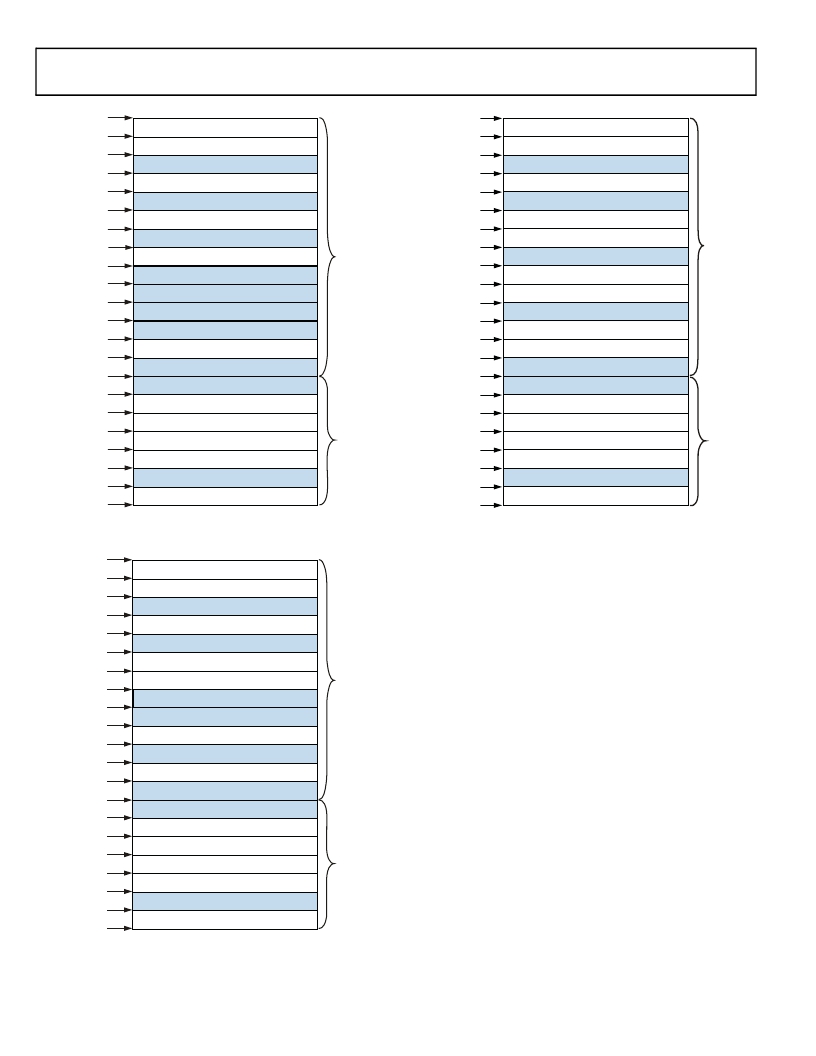

�0xFFFF� FFFF�

�0xFFFF� FFFF�

�CORE� MMR� REGISTERS� (2M� BYTE)�

�0xFFE0� 0000�

�SYSTEM� MMR� REGISTERS� (2M� BYTE)�

�0xFFC0� 0000�

�RESERVED�

�0xFFB0� 1000�

�SCRATCHPAD� SRAM� (4K� BYTE)�

�0xFFB0 0000�

�RESERVED�

�0xFFA1� 4000�

�INSTRUCTION� SRAM/CACHE� (16K� BYTE)�

�0xFFA1� 0000�

�INSTRUCTION� SRAM� (64K� BYTE)�

�0xFFA0� 0000�

�RESERVED�

�0xFF90� 8000�

�DATA� BANK� B� SRAM/CACHE� (16K� BYTE)�

�0xFF90� 4000�

�DATA� BANK� B� SRAM� (16K� BYTE)�

�0xFF90� 0000�

�RESERVED�

�0xFF80� 8000�

�DATA� BANK� A� SRAM/CACHE� (16K� BYTE)�

�0xFF80� 4000�

�DATA� BANK� A� SRAM� (16K� BYTE)�

�0xFF80� 0000�

�RESERVED�

�0xEF00� 0000�

�RESERVED�

�0x2040� 0000�

�ASYNC� MEMORY� BANK� 3� (1M� BYTE)�

�0x2030� 0000�

�ASYNC� MEMORY� BANK� 2� (1M� BYTE)�

�0x2020� 0000�

�ASYNC� MEMORY� BANK� 1� (1M� BYTE)�

�0x2010� 0000�

�ASYNC� MEMORY� BANK� 0� (1M� BYTE)�

�0x2000� 0000�

�RESERVED�

�0x0800� 0000�

�SDRAM� MEMORY� (16M� BYTE� TO� 128M� BYTE)�

�0x0000� 0000�

�Figure� 5.� ADSP-BF533� Internal/External� Memory� Map�

�Event� Handling�

�0xFFE0� 0000�

�0xFFC0� 0000�

�0xFFB0� 1000�

�0xFFB0� 0000�

�0xFFA1� 4000�

�0xFFA1� 0000�

�0xFFA0� 8000�

�0xFFA0� 0000�

�0xFF90� 8000�

�0xFF90 4000�

�0xFF80� 8000�

�0xFF80� 4000�

�0xEF00� 0000�

�0x2040� 0000�

�0x2030� 0000�

�0x2020� 0000�

�0x2010� 0000�

�0x2000� 0000�

�0x0800� 0000�

�0x0000� 0000�

�CORE� MMR� REGISTERS� (2M� BYTE)�

�SYSTEM� MMR� REGISTERS� (2M� BYTE)�

�RESERVED�

�SCRATCHPAD� SRAM� (4K� BYTE)�

�RESERVED�

�INSTRUCTION� SRAM/CACHE� (16K� BYTE)�

�INSTRUCTION� SRAM� (32K� BYTE)�

�RESERVED�

�RESERVED�

�DATA� BANK� B� SRAM/CACHE� (16K� BYTE)�

�RESERVED�

�DATA� BANK� A� SRAM/CACHE� (16K� BYTE)�

�RESERVED�

�RESERVED�

�ASYNC� MEMORY� BANK� 3� (1M� BYTE)�

�ASYNC� MEMORY� BANK� 2� (1M� BYTE)�

�ASYNC� MEMORY� BANK� 1� (1M� BYTE)�

�ASYNC� MEMORY� BANK� 0� (1M� BYTE)�

�RESERVED�

�SDRAM� MEMORY� (16M� BYTE� TO� 128M� BYTE)�

�The� event� controller� on� the� processors� handle� all� asynchronous�

�and� synchronous� events� to� the� processor.� The� ADSP-BF531/�

�ADSP-BF532/ADSP-BF533� processors� provide� event� handling�

�that� supports� both� nesting� and� prioritization.� Nesting� allows�

�multiple� event� service� routines� to� be� active� simultaneously.� Pri-�

�oritization� ensures� that� servicing� of� a� higher� priority� event� takes�

�precedence� over� servicing� of� a� lower� priority� event.� The� control-�

�ler� provides� support� for� five� different� types� of� events:�

�?� Emulation� –� An� emulation� event� causes� the� processor� to�

�enter� emulation� mode,� allowing� command� and� control� of�

�the� processor� via� the� JTAG� interface.�

�?� Reset� –� This� event� resets� the� processor.�

�?� Nonmaskable� Interrupt� (NMI)� –� The� NMI� event� can� be�

�generated� by� the� software� watchdog� timer� or� by� the� NMI�

�input� signal� to� the� processor.� The� NMI� event� is� frequently�

�used� as� a� power-down� indicator� to� initiate� an� orderly� shut-�

�down� of� the� system.�

�?� Exceptions� –� Events� that� occur� synchronously� to� program�

�flow� (i.e.,� the� exception� is� taken� before� the� instruction� is�

�allowed� to� complete).� Conditions� such� as� data� alignment�

�violations� and� undefined� instructions� cause� exceptions.�

�?� Interrupts� –� Events� that� occur� asynchronously� to� program�

�flow.� They� are� caused� by� input� pins,� timers,� and� other�

�Figure� 4.� ADSP-BF532� Internal/External� Memory� Map�

�peripherals,� as� well� as� by� an� explicit� software� instruction.�

�Rev.� I�

�|�

�Page� 6� of� 64� |�

�August� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6504UKP005+T | IC TEMP SWITCH SOT23-5 |

| TPSB476K010A0250 | CAP TANT 47UF 10V 10% 1210 |

| TPSB476K006H0500 | CAP TANT 47UF 6.3V 10% 1210 |

| VI-B63-EU-B1 | CONVERTER MOD DC/DC 24V 200W |

| VI-B4X-EU-B1 | CONVERTER MOD DC/DC 5.2V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF531SBBCZC74 | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBCZC92 | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBCZENG | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBZ400 | 功能描述:IC DSP CTLR 16BIT 400MHZ 169BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF531SBST-300 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。