- 您现在的位置:买卖IC网 > PDF目录19389 > ADSP-BF533SBBC500 (Analog Devices Inc)IC DSP CTLR 16B 500MHZ 160CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF533SBBC500 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16B 500MHZ 160CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | SPI,SSP,UART |

| 时钟速率: | 500MHz |

| 非易失内存: | ROM(1 kB) |

| 芯片上RAM: | 148kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-LFBGA,CSPBGA |

| 供应商设备封装: | 160-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT ADZS-BF533-EZLITE-ND - KIT W/BOARD EVAL FOR ADSP-BF533 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�ADSP-BF531� /� ADSP-BF532� /� ADSP-BF533�

�Each� event� type� has� an� associated� register� to� hold� the� return�

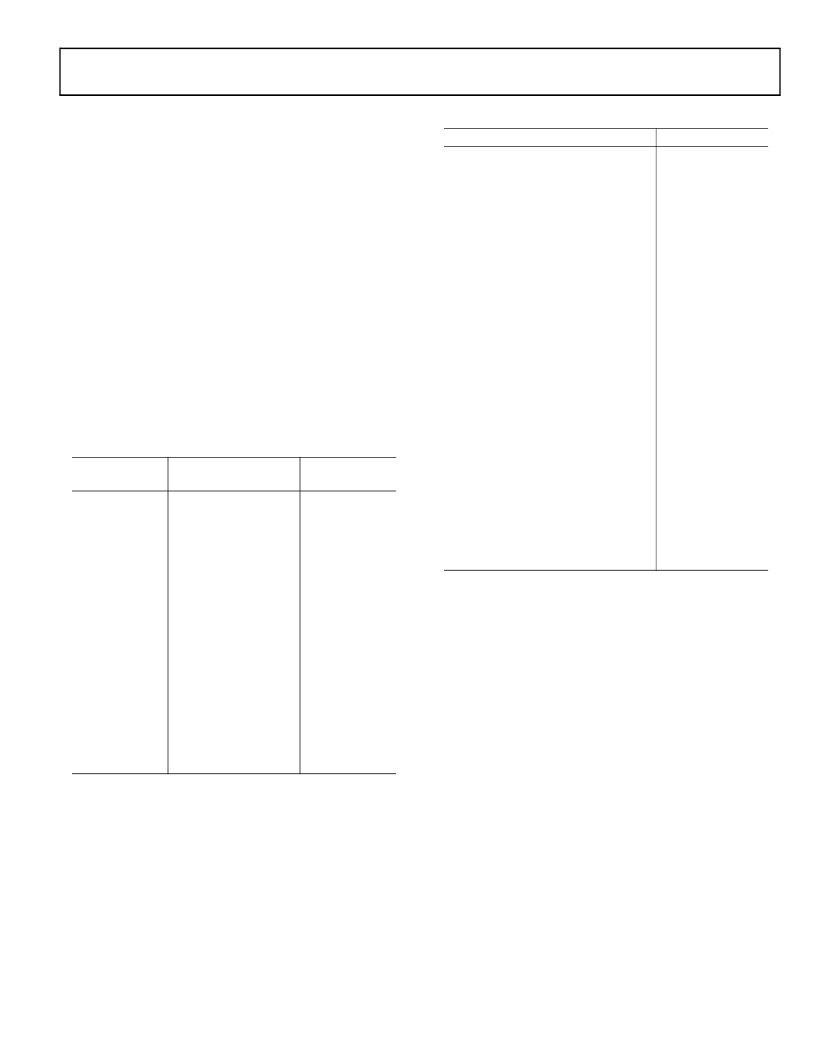

�Table� 3.� System� Interrupt� Controller� (SIC)�

�address� and� an� associated� return-from-event� instruction.� When�

�an� event� is� triggered,� the� state� of� the� processor� is� saved� on� the�

�supervisor� stack.�

�The� ADSP-BF531/ADSP-BF532/ADSP-BF533� processors’� event�

�controller� consists� of� two� stages,� the� core� event� controller� (CEC)�

�and� the� system� interrupt� controller� (SIC).� The� core� event� con-�

�troller� works� with� the� system� interrupt� controller� to� prioritize�

�and� control� all� system� events.� Conceptually,� interrupts� from� the�

�peripherals� enter� into� the� SIC,� and� are� then� routed� directly� into�

�the� general-purpose� interrupts� of� the� CEC.�

�Core� Event� Controller� (CEC)�

�The� CEC� supports� nine� general-purpose� interrupts� (IVG15� –7),�

�in� addition� to� the� dedicated� interrupt� and� exception� events.� Of�

�these� general-purpose� interrupts,� the� two� lowest� priority� inter-�

�rupts� (IVG15� –14)� are� recommended� to� be� reserved� for� software�

�interrupt� handlers,� leaving� seven� prioritized� interrupt� inputs� to�

�support� the� peripherals� of� the� processor.� Table� 2� describes� the�

�inputs� to� the� CEC,� identifies� their� names� in� the� event� vector�

�table� (EVT),� and� lists� their� priorities.�

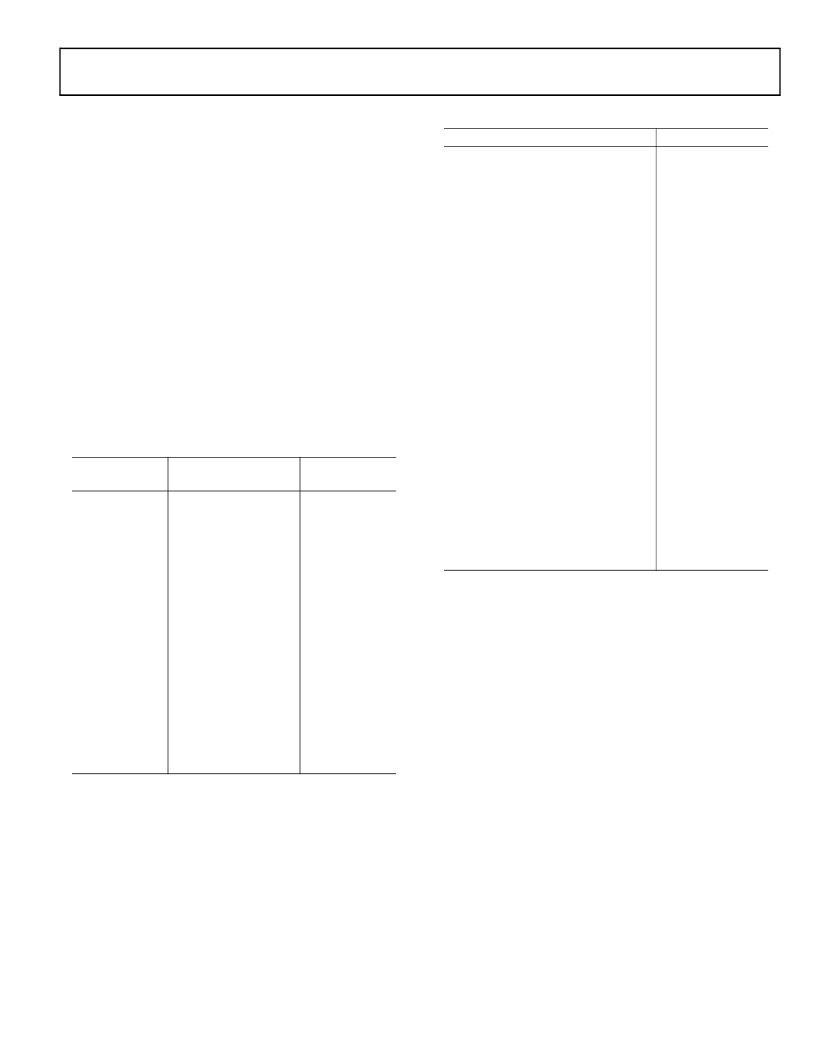

�Table� 2.� Core� Event� Controller� (CEC)�

�Peripheral� Interrupt� Event�

�PLL� Wakeup�

�DMA� Error�

�PPI� Error�

�SPORT� 0� Error�

�SPORT� 1� Error�

�SPI� Error�

�UART� Error�

�Real-Time� Clock�

�DMA� Channel� 0� (PPI)�

�DMA� Channel� 1� (SPORT� 0� Receive)�

�DMA� Channel� 2� (SPORT� 0� Transmit)�

�DMA� Channel� 3� (SPORT� 1� Receive)�

�DMA� Channel� 4� (SPORT� 1� Transmit)�

�DMA� Channel� 5� (SPI)�

�DMA� Channel� 6� (UART� Receive)�

�DMA� Channel� 7� (UART� Transmit)�

�Timer� 0�

�Default� Mapping�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG8�

�IVG8�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG10�

�IVG10�

�IVG10�

�IVG11�

�Priority�

�(0� is� Highest)�

�0�

�1�

�2�

�3�

�4�

�Event� Class�

�Emulation/Test� Control�

�Reset�

�Nonmaskable� Interrupt�

�Exception�

�Reserved�

�EVT� Entry�

�EMU�

�RST�

�NMI�

�EVX�

�Timer� 1�

�Timer� 2�

�Port� F� GPIO� Interrupt� A�

�Port� F� GPIO� Interrupt� B�

�Memory� DMA� Stream� 0�

�Memory� DMA� Stream� 1�

�Software� Watchdog� Timer�

�IVG11�

�IVG11�

�IVG12�

�IVG12�

�IVG13�

�IVG13�

�IVG13�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�Hardware� Error�

�Core� Timer�

�General� Interrupt� 7�

�General� Interrupt� 8�

�General� Interrupt� 9�

�General� Interrupt� 10�

�General� Interrupt� 11�

�General� Interrupt� 12�

�General� Interrupt� 13�

�General� Interrupt� 14�

�General� Interrupt� 15�

�IVHW�

�IVTMR�

�IVG7�

�IVG8�

�IVG9�

�IVG10�

�IVG11�

�IVG12�

�IVG13�

�IVG14�

�IVG15�

�Event� Control�

�The� processors� provide� a� very� flexible� mechanism� to� control� the�

�processing� of� events.� In� the� CEC,� three� registers� are� used� to�

�coordinate� and� control� events.� Each� register� is� 32� bits� wide:�

�?� CEC� interrupt� latch� register� (ILAT)� –� The� ILAT� register�

�indicates� when� events� have� been� latched.� The� appropriate�

�bit� is� set� when� the� processor� has� latched� the� event� and�

�cleared� when� the� event� has� been� accepted� into� the� system.�

�This� register� is� updated� automatically� by� the� controller,� but�

�it� can� also� be� written� to� clear� (cancel)� latched� events.� This�

�register� can� be� read� while� in� supervisor� mode� and� can� only�

�be� written� while� in� supervisor� mode� when� the� correspond-�

�ing� IMASK� bit� is� cleared.�

�System� Interrupt� Controller� (SIC)�

�The� system� interrupt� controller� provides� the� mapping� and� rout-�

�ing� of� events� from� the� many� peripheral� interrupt� sources� to� the�

�prioritized� general-purpose� interrupt� inputs� of� the� CEC.�

�Although� the� processors� provide� a� default� mapping,� the� user�

�can� alter� the� mappings� and� priorities� of� interrupt� events� by� writ-�

�ing� the� appropriate� values� into� the� interrupt� assignment�

�registers� (SIC_IARx).� Table� 3� describes� the� inputs� into� the� SIC�

�and� the� default� mappings� into� the� CEC.�

�?� CEC� interrupt� mask� register� (IMASK)� –� The� IMASK� regis-�

�ter� controls� the� masking� and� unmasking� of� individual�

�events.� When� a� bit� is� set� in� the� IMASK� register,� that� event� is�

�unmasked� and� is� processed� by� the� CEC� when� asserted.� A�

�cleared� bit� in� the� IMASK� register� masks� the� event,�

�preventing� the� processor� from� servicing� the� event� even�

�though� the� event� may� be� latched� in� the� ILAT� register.� This�

�register� can� be� read� or� written� while� in� supervisor� mode.�

�Note� that� general-purpose� interrupts� can� be� globally�

�enabled� and� disabled� with� the� STI� and� CLI� instructions,�

�respectively.�

�Rev.� I�

�|�

�Page� 7� of� 64� |�

�August� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6644LBAAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

| ADSP-2105BP-80 | IC DSP CONTROLLER 16BIT 68PLCC |

| ADSP-BF542MBBCZ-5M | IC DSP 16BIT 533MHZ MDDR 400CBGA |

| ADSP-BF525KBCZ-5C2 | IC DSP CTRLR 16B W/CODEC 289BGA |

| ADSP-21266SKBCZ-2D | IC DSP 32BIT 200MHZ 136-CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSPBF533SBBC-500 | 制造商:Analog Devices 功能描述:Dual MAC16-bit500MHz 148KB SRAM |

| ADSPBF533SBBC500X | 制造商:Analog Devices 功能描述: |

| ADSP-BF533SBBC-500X | 制造商:Analog Devices 功能描述: |

| ADSP-BF533SBBC-5V | 功能描述:IC DSP CTLR DUAL 160CSPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF533SBBC-C10 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。