- 您现在的位置:买卖IC网 > PDF目录19473 > ADSP-BF548MBBCZ-5M (Analog Devices Inc)IC DSP 533MHZ W/DDR 400CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF548MBBCZ-5M |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/100页 |

| 文件大小: | 0K |

| 描述: | IC DSP 533MHZ W/DDR 400CSPBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART,USB |

| 时钟速率: | 533MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 260kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.25V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 400-LFBGA,CSPBGA |

| 供应商设备封装: | 400-CSPBGA(17x17) |

| 包装: | 托盘 |

| 配用: | ADSP-3PARCBF548M01-ND - MODULE BOARD BF548 ADSP-3PARCBF548E02-ND - KIT DEV STARTER BF548 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

Rev. C

|

Page 35 of 100

|

February 2010

ments for the ADSP-BF54x Blackfin processors’ clocks. Take

care in selecting MSEL, SSEL, and CSEL ratios so as not to

exceed the maximum core clock and system clock. Table 15

describes the phase-locked loop operating conditions.

7 Parameter value applies to pins DQ0–15 and DQS0–1.

8 PB1-0, PE15-14, PG15-11, and PH7-6 are 5.0 V-tolerant (always accept up to 5.5 V maximum V

IH when power is applied to VDDEXT pins). Voltage compliance (on output

VOH) is limited by VDDEXT supply voltage.

9 SDA and SCL are 5.0V tolerant (always accept up to 5.5V maximum V

IH). Voltage compliance on outputs (VOH) is limited by the VDDEXT supply voltage.

10Parameter value applies to USB_DP, USB_DM, and USB_VBUS pins. See Absolute Maximum Ratings on Page 40.

11Parameter value applies to all input and bidirectional pins, except PB1-0, PE15-14, PG15–11, and PH7-6.

12Parameter value applies to pins PG15–11 and PH7-6.

13Parameter value applies to pins PB1-0 and PE15-14. Consult the I2C specification version 2.1 for the proper resistor value and other open drain pin electrical parameters.

14TJ must be in the range: 0°C < TJ < 55°C during OTP memory programming operations.

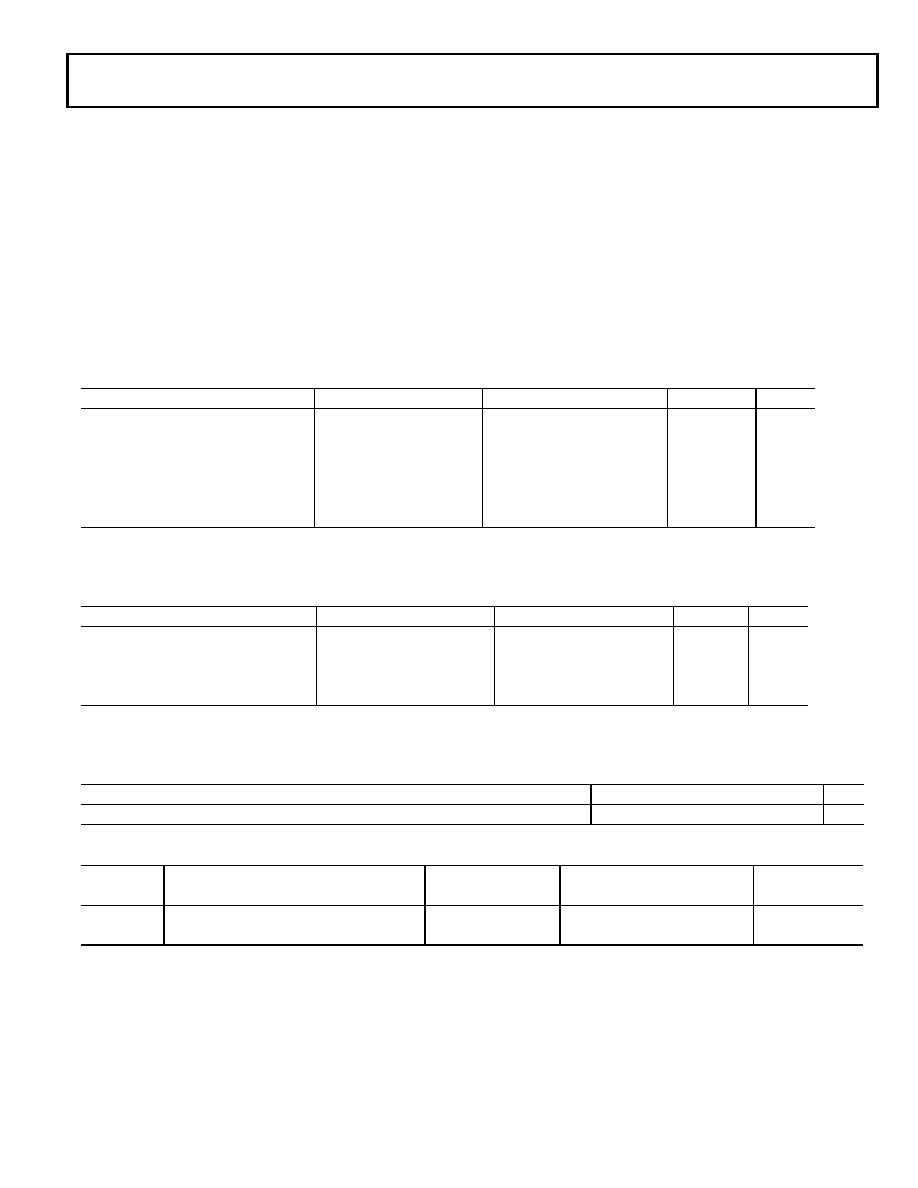

Table 13. Core Clock Requirements—533 MHz and 600 MHz Speed Grade1

Parameter

Condition

Internal Regulator Setting2

Max

Unit

fCCLK

Core Clock Frequency

VDDINT = 1.30 V minimum

600

MHz

fCCLK

Core Clock Frequency

VDDINT = 1.20 V minimum

1.25 V

533

MHz

fCCLK

Core Clock Frequency

VDDINT = 1.14 V minimum

1.20 V

500

MHz

fCCLK

Core Clock Frequency

VDDINT = 1.045 V minimum

1.10 V

444

MHz

fCCLK

Core Clock Frequency

VDDINT = 0.95 V minimum

1.00 V

400

MHz

fCCLK

Core Clock Frequency

VDDINT = 0.90 Vminimum

0.95 V

333

MHz

1 See the Ordering Guide on Page 100.

2 Use of an internal voltage regulator is not supported on automotive grade and 600 MHz speed grade models

Table 14. Core Clock Requirements—400 MHz Speed Grade1

Parameter

Condition

Internal Regulator Setting2

Max

Unit

fCCLK

Core Clock Frequency

VDDINT = 1.14 V minimum

1.20 V

400

MHz

fCCLK

Core Clock Frequency

VDDINT = 1.045 V minimum

1.10 V

364

MHz

fCCLK

Core Clock Frequency

VDDINT = 0.95 V minimum

1.00 V

333

MHz

fCCLK

Core Clock Frequency

VDDINT = 0.90 V minimum

0.95 V

300

MHz

2 Use of an internal voltage regulator is not supported on automotive grade models

Table 15. Phase-Locked Loop Operating Conditions

Parameter

Min

Max

Unit

fVCO

Voltage Controlled Oscillator (VCO) Frequency

50

Maximum fCCLK

MHz

Table 16. System Clock Requirements

Parameter

Condition

DDR SDRAM Models

Mobile DDR SDRAM Models

Unit

Max

Min

Max

fSCLK

VDDINT ≥ 1.14 V

1

1332

1203

1332

MHz

fSCLK

100

N/A4

N/A4

MHz

1 f

SCLK must be less than or equal to fCCLK.

2 Rounded number. Actual test specification is SCLK period of 7.5 ns. See Table 26 on Page 43.

3 Rounded number. Actual test specification is SCLK period of 8.33 ns.

4 VDDINT must be greater than or equal to 1.14 V for mobile DDR SDRAM models. See Operating Conditions on Page 34.

相关PDF资料 |

PDF描述 |

|---|---|

| SG5841JSY | IC CTLR PWM HI INTEGRATED 8-SOIC |

| TAJB476K010B | CAP TANT 47UF 10V 10% 1210 |

| MIC184YMM TR | IC SUPERVISOR LOCAL/REMOTE 8MSOP |

| ADSP-BF548BBCZ-5A | IC DSP 16BIT 533MHZ 400CSBGA |

| ACM36DRKS | CONN EDGECARD 72POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF549BBCZ | 制造商:Analog Devices 功能描述: |

| ADSP-BF549BBCZ-ENG | 制造商:Analog Devices 功能描述:- Bulk |

| adsp-bf5615bbz600 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| ADSP-BF561KBCZ-600 | 制造商:Analog Devices 功能描述: |

| ADSP-BF561SBB500 | 功能描述:IC PROCESSOR 500MHZ 297PBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。