- 您现在的位置:买卖IC网 > PDF目录19473 > ADSP-BF548MBBCZ-5M (Analog Devices Inc)IC DSP 533MHZ W/DDR 400CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF548MBBCZ-5M |

| 厂商: | Analog Devices Inc |

| 文件页数: | 82/100页 |

| 文件大小: | 0K |

| 描述: | IC DSP 533MHZ W/DDR 400CSPBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART,USB |

| 时钟速率: | 533MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 260kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.25V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 400-LFBGA,CSPBGA |

| 供应商设备封装: | 400-CSPBGA(17x17) |

| 包装: | 托盘 |

| 配用: | ADSP-3PARCBF548M01-ND - MODULE BOARD BF548 ADSP-3PARCBF548E02-ND - KIT DEV STARTER BF548 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页当前第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

Rev. C

|

Page 82 of 100

|

February 2010

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

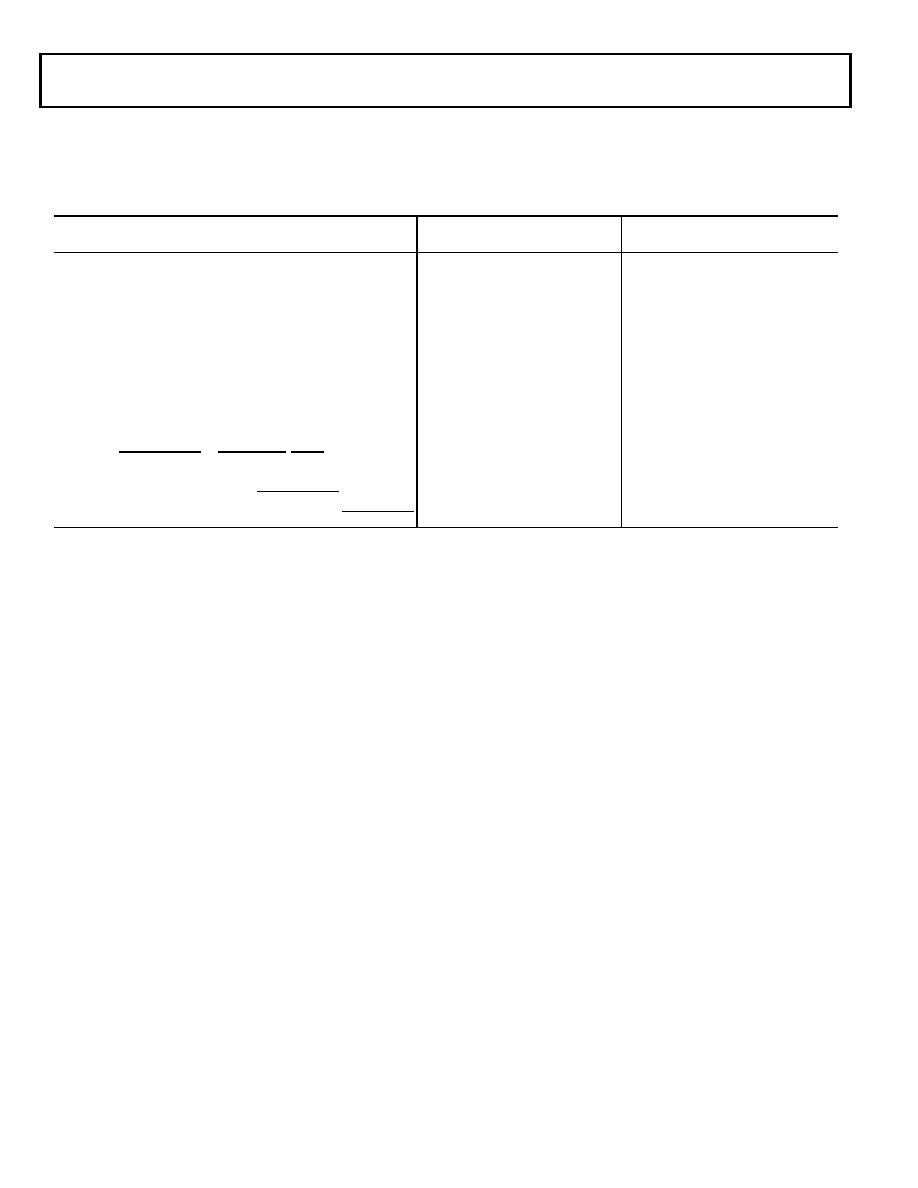

ATAPI Ultra DMA Data-Out Transfer Timing

ultra DMA data-out transfer timing.

Table 61. ATAPI Ultra DMA Data-Out Transfer Timing

ATAPI Parameter

ATAPI_ULTRA_TIM_x Timing

Register Setting1

Timing Equation

tCYC

2

Cycle time

TDVS, TCYC_TDVS

(TDVS + TCYC_TDVS)

× t

SCLK

t2CYC

Two cycle time

TDVS, TCYC_TDVS

2

× (TDVS + TCYC_TDVS) × t

SCLK

tDVS

Data valid setup time at sender

TDVS

× t

SCLK – (tSK1 + tSK2)

tDVH

Data valid hold time at sender

TCYC_TDVS

× t

SCLK – (tSK1 + tSK2)

tCVS

CRC word valid setup time at host

TDVS

× t

SCLK – (tSK1 + tSK2)

tCVH

CRC word valid hold time at host

TACK

× t

SCLK – (tSK1 + tSK2)

tDZFS

Time from data output released-to-driving to first

strobe timing

TDVS

× t

SCLK – (tSK1 + tSK2)

tLI

Limited interlock time

N/A

2

× t

BD + 2 × tSCLK + tOD

tMLI

Interlock time with minimum

TMLI

× t

SCLK – (tSK1 + tSK2)

tENV

3

ATAPI_DMACK to ATAPI_DIOR/DIOW

TENV

(TENV

× t

SCLK) +/– (tSK1 + tSK2)

tRFS

Ready to final strobe time

N/A

2

× t

BD + 2 × tSCLK + tOD

tACK

Setup and Hold time for ATAPI_DMACK

TACK

× t

SCLK – (tSK1 + tSK2)

tSS

Time from STROBE edge to assertion of ATAPI_DIOW TSS

TSS

× t

SCLK – (tSK1 + tSK2)

1 ATAPI Timing Register Setting should be programmed with a value that guarantees parameter compliance with the ATA ANSI specification for ATA device mode of operation.

2 ATA/ATAPI-6 compliant functionality with limited speed.

3 This timing equation can be used to calculate both the minimum and maximum t

ENV.

相关PDF资料 |

PDF描述 |

|---|---|

| SG5841JSY | IC CTLR PWM HI INTEGRATED 8-SOIC |

| TAJB476K010B | CAP TANT 47UF 10V 10% 1210 |

| MIC184YMM TR | IC SUPERVISOR LOCAL/REMOTE 8MSOP |

| ADSP-BF548BBCZ-5A | IC DSP 16BIT 533MHZ 400CSBGA |

| ACM36DRKS | CONN EDGECARD 72POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF549BBCZ | 制造商:Analog Devices 功能描述: |

| ADSP-BF549BBCZ-ENG | 制造商:Analog Devices 功能描述:- Bulk |

| adsp-bf5615bbz600 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| ADSP-BF561KBCZ-600 | 制造商:Analog Devices 功能描述: |

| ADSP-BF561SBB500 | 功能描述:IC PROCESSOR 500MHZ 297PBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。