- 您现在的位置:买卖IC网 > PDF目录166232 > AS5SS256K18DQ-8IT (Austin Semiconductor, Inc) 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through PDF资料下载

参数资料

| 型号: | AS5SS256K18DQ-8IT |

| 厂商: | Austin Semiconductor, Inc |

| 英文描述: | 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| 中文描述: | 256 × 18的SSRAM同步突发静态存储器,流通过 |

| 文件页数: | 13/13页 |

| 文件大小: | 225K |

| 代理商: | AS5SS256K18DQ-8IT |

AS5SS256K18

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

9

SSRAM

AS5SS256K18

Austin Semiconductor, Inc.

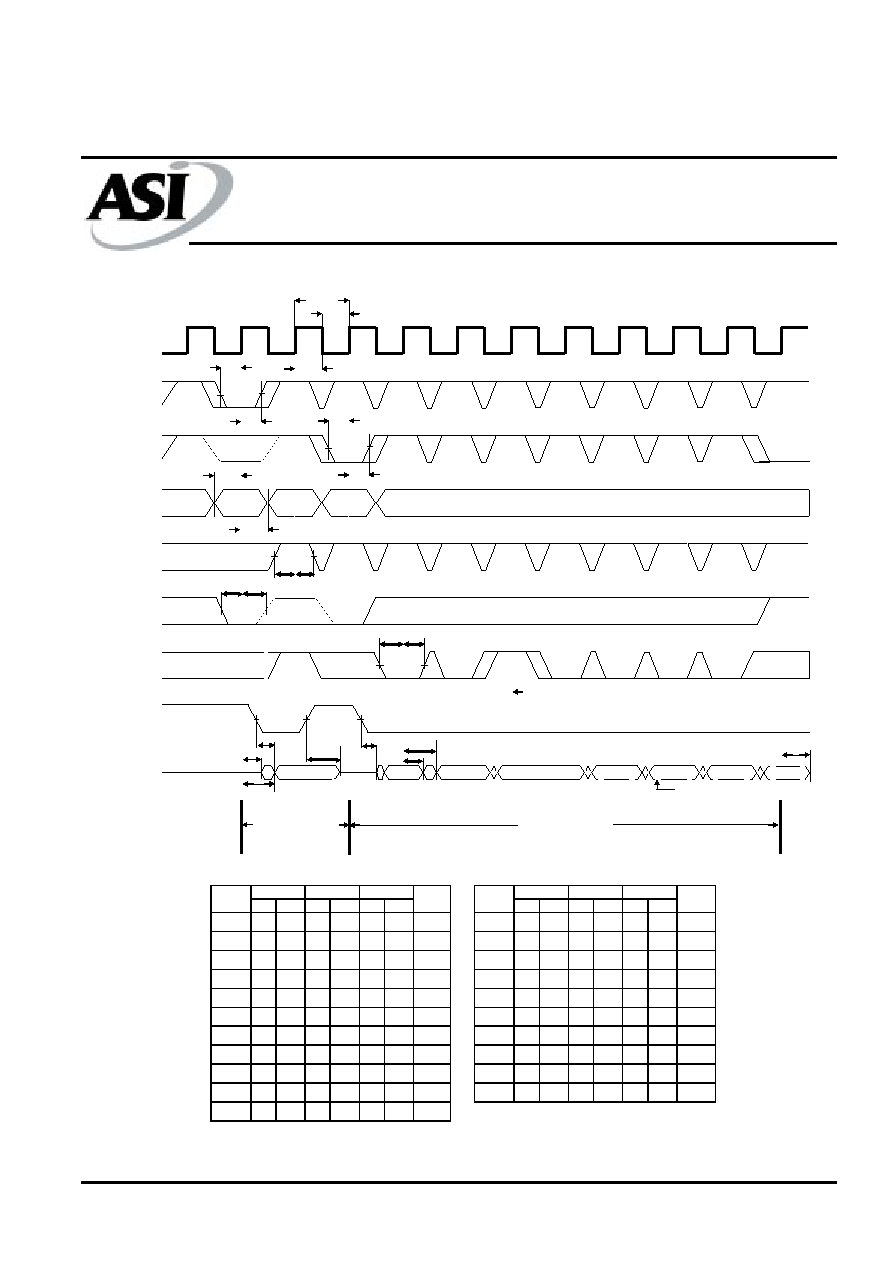

READ TIMING

NOTE: 1. Q(A2) referes to output from address A2. Q(A2+1) refers to output from the next internal burst address following A2.

2. CE2\ and CE2 have timing identical to CE\. On this diagram, when CE\ is LOW, CE2\ is LOW and CE2 is HIGH. When CE\ is HIGH, CE2\ is HIGH and CE2 is LOW.

3. Timing is shown assuming that the device was not enabled before entering into this sequence.

4. Outputs are disabled t

KQHZ

after deselect.

READ TIMING PARAMETERS

MIN MAX MIN MAX MIN MAX

tKC

8.8

10

15

ns

tAS

1.5

1.8

2.0

ns

tKF

113

100

66

MHz

tADSS

1.5

1.8

2.0

ns

tKH

2.5

3.0

4.0

ns

tAAS

1.5

1.8

2.0

ns

tKL

2.5

3.0

4.0

ns

tWS

1.5

1.8

2.0

ns

tKQ

7.5

8.5

10

ns

tCES

1.5

1.8

2.0

ns

tKQX

1.5

3.0

ns

tAH

0.5

ns

tKQLZ

1.5

3.0

ns

tADSH

0.5

ns

tKQHZ

4.2

5.0

ns

tAAH

0.5

ns

tOEQ

4.2

5.0

ns

tWH

0.5

ns

tOELZ

000

ns

tCEH

0.5

ns

tOEHZ

4.2

5.0

ns

-10

-9

-8

SYM

-10

UNITS

SYM

-8

-9

1234567890123

1234

123456789

1234

12345

123456

1234567890123456

12345

123456789

12345

1234567

1

CLK

ADSP\

ADSC\

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○

○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○

○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○

ADDRESS

A2

BWE\, GW\,

BWa\-BWb\

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○

CE\

(Note 2)

ADV\

OE\

SINGLE READ

BURST READ

○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

Q

12345

A1

12345678

123

12345678

12345678901234567890123456789012123456789012345678901234567890121234567890123456789

12

Q(A2)

Q(A2+2)

12

Q(A2+3)

12

Q(A2)

123

Q(A2+1)

12

Q(A2+2)

123456

1234567

123456

12345

123456

12345

123456

12345678

12

123456

12345

123456

Q(A1)

Q(A2+1)

123456

1234567

123456

1234567890123456789012

12

123456

123456789012345678901234567890121234567890123456789012345678901212345678901234567

123456

1234567890123456789012

12

123456789012

123456

1

123

1234

t

ADSS

t

ADSH

123456

t

AS

t

AH

t

KC

t

KL

t

KH

t

ADSS

t

ADSH

t

WS tWH

t

CES tCEH

123456

t

AAS

t

AAH

ADV\ suspends burst.

High-Z

t

OEHZ

t

KQLZ

t

KQ

t

OEQ

t

OELZ

t

KQ

t

KQX

t

KQHZ

Burst wraps around

to its initial state.

(NOTE 1)

Deselect Cycle

(Note 4)

相关PDF资料 |

PDF描述 |

|---|---|

| AS5SS256K36ADQ-8.5/883C | 256K x 36 SSRAM Flow-Through, Synchronous Burst SRAM |

| AS6054 | 1000 MHz - 6000 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

| AS7C1028-15JC | 256K X 4 STANDARD SRAM, 15 ns, PDSO28 |

| AS7C25512FT32A-85BIN | 512K X 32 STANDARD SRAM, 8.5 ns, PBGA165 |

| AS7C25512NTD32A-166TQI | 512K X 32 ZBT SRAM, 3.5 ns, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AS5SS256K18DQ-9 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-9/IT | 制造商:AUSTIN 制造商全称:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-9/XT | 制造商:AUSTIN 制造商全称:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K36 | 制造商:AUSTIN 制造商全称:Austin Semiconductor 功能描述:256K x 36 SSRAM Flow-Through, Synchronous Burst SRAM |

| AS5SS256K36_05 | 制造商:AUSTIN 制造商全称:Austin Semiconductor 功能描述:256K x 36 SSRAM Flow-Through, Synchronous Burst SRAM |

发布紧急采购,3分钟左右您将得到回复。