- 您现在的位置:买卖IC网 > PDF目录20558 > AT25256W-10SI-2.7 (Atmel)IC EEPROM 256KBIT 3MHZ 8SOIC PDF资料下载

参数资料

| 型号: | AT25256W-10SI-2.7 |

| 厂商: | Atmel |

| 文件页数: | 5/22页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 256KBIT 3MHZ 8SOIC |

| 标准包装: | 94 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 256K (32K x 8) |

| 速度: | 2.1MHz,3MHz |

| 接口: | SPI 3 线串行 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

�� �

�

�

�AT25128/256�

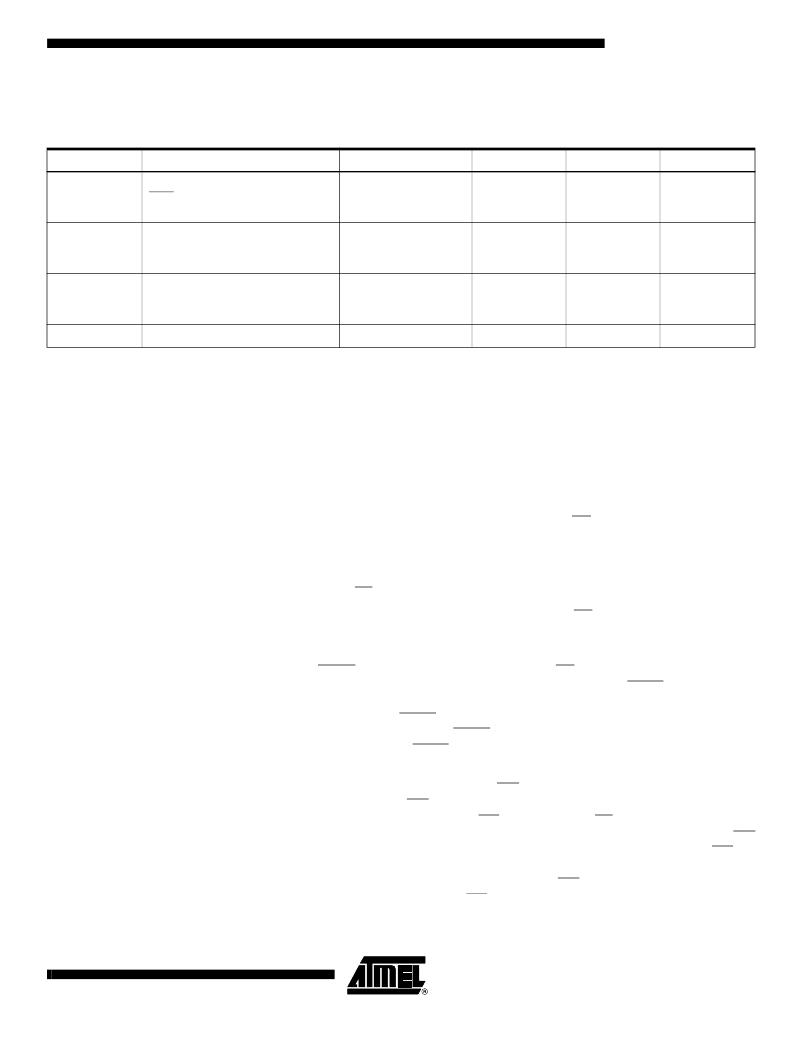

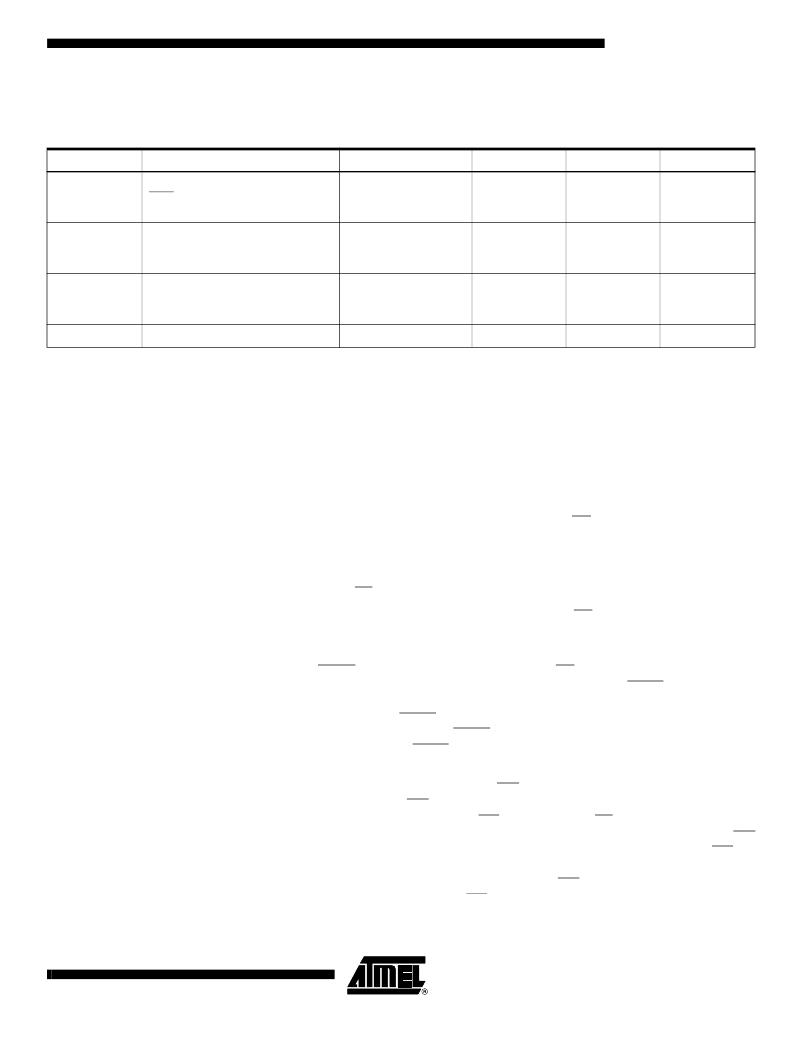

�Table� 4.� AC� Characteristics� (Continued)�

�Applicable� over� recommended� operating� range� from� T� AI� =� –� 40� °� C� to� +� 85� °� C,� T� AE� =� –� 40� °� C� to� +125� °� C,� V� CC� =� As� Specified,�

�CL� =� 1� TTL� Gate� and� 100� pF� (unless� otherwise� noted)�

�Symbol�

�Parameter�

�Voltage�

�Min�

�Max�

�Units�

�4.5� –� 5.5�

�100�

�t� HZ�

�Hold� to� Output� High� Z�

�2.7� –� 5.5�

�200�

�ns�

�1.8� –� 5.5�

�4.5� –� 5.5�

�300�

�200�

�t� DIS�

�Output� Disable� Time�

�2.7� –� 5.5�

�250�

�ns�

�1.8� –� 5.5�

�4.5� –� 5.5�

�1000�

�5�

�t� WC�

�Write� Cycle� Time�

�2.7� –� 5.5�

�10�

�ms�

�1.8� –� 5.5�

�10�

�Endurance� (1)�

�5.0V,� 25� °� C,� Page� Mode�

�100K�

�Write� Cycles�

�Note:�

�1.� This� parameter� is� characterized� and� is� not� 100%� tested.� Contact� Atmel� for� further� information.�

�Serial� Interface�

�Description�

�MASTER:�

�SLAVE:�

�The� device� that� generates� the� serial� clock.�

�Because� the� serial� clock� pin� (SCK)� is� always� an� input,� the� AT25128/256�

�always� operates� as� a� slave.�

�TRANSMITTER/RECEIVER:� The� AT25128/256� has� separate� pins� designated� for� data�

�transmission� (SO)� and� reception� (SI).�

�MSB:�

�The� Most� Significant� Bit� (MSB)� is� the� first� bit� transmitted� and� received.�

�SERIAL� OP-CODE:�

�After� the� device� is� selected� with� CS� going� low,� the� first� byte� will�

�be� received.� This� byte� contains� the� op-code� that� defines� the� operations� to� be� performed.�

�INVALID� OP-CODE:�

�If� an� invalid� op-code� is� received,� no� data� will� be� shifted� into� the�

�AT25128/256,� and� the� serial� output� pin� (SO)� will� remain� in� a� high� impedance� state� until�

�the� falling� edge� of� CS� is� detected� again.� This� will� reinitialize� the� serial� communication.�

�CHIP� SELECT:� The� AT25128/256� is� selected� when� the� CS� pin� is� low.� When� the� device�

�is� not� selected,� data� will� not� be� accepted� via� the� SI� pin,� and� the� serial� output� pin� (SO)�

�will� remain� in� a� high� impedance� state.�

�HOLD:� The� HOLD� pin� is� used� in� conjunction� with� the� CS� pin� to� select� the� AT25128/256.�

�When� the� device� is� selected� and� a� serial� sequence� is� underway,� HOLD� can� be� used� to�

�pause� the� serial� communication� with� the� master� device� without� resetting� the� serial�

�sequence.� To� pause,� the� HOLD� pin� must� be� brought� low� while� the� SCK� pin� is� low.� To�

�resume� serial� communication,� the� HOLD� pin� is� brought� high� while� the� SCK� pin� is� low�

�(SCK� may� still� toggle� during� HOLD).� Inputs� to� the� SI� pin� will� be� ignored� while� the� SO� pin�

�is� in� the� high� impedance� state.�

�WRITE� PROTECT:� The� write� protect� pin� (WP)� will� allow� normal� read/write� operations�

�when� held� high.� When� the� WP� pin� is� brought� low� and� WPEN� bit� is� “1”,� all� write� opera-�

�tions� to� the� status� register� are� inhibited.� WP� going� low� while� CS� is� still� low� will� interrupt� a�

�write� to� the� status� register.� If� the� internal� write� cycle� has� already� been� initiated,� WP�

�going� low� will� have� no� effect� on� any� write� operation� to� the� status� register.� The� WP� pin�

�function� is� blocked� when� the� WPEN� bit� in� the� status� register� is� “0”.� This� will� allow� the�

�user� to� install� the� AT25128/256� in� a� system� with� the� WP� pin� tied� to� ground� and� still� be�

�able� to� write� to� the� status� register.� All� WP� pin� functions� are� enabled� when� the� WPEN� bit�

�is� set� to� “1”.�

�5�

�0872O–SEEPR–03/05�

�相关PDF资料 |

PDF描述 |

|---|---|

| AT25256W-10SI-1.8 | IC EEPROM 256KBIT 2.1MHZ 8SOIC |

| LXC75-0350SW | POWER SUPPLY LED 75W 350MA |

| T95V335M020CSAL | CAP TANT 3.3UF 20V 20% 1410 |

| VE-2NJ-CY-B1 | CONVERTER MOD DC/DC 36V 50W |

| LDV75-024SN | POWER SUPPLY LED 75W 24V COMPACT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT25256W-10SJ-1.8 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:SPI Serial EEPROMs |

| AT25256W-10SJ-2.7 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:SPI Serial EEPROMs |

| AT25256W10SU27 | 制造商:ATMEL 功能描述:Pb Free |

| AT-252PIN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog Attenuator |

| AT25320 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:SPI Serial EEPROMs |

发布紧急采购,3分钟左右您将得到回复。