参数资料

| 型号: | AT80C51RA2-SLSUL |

| 厂商: | Atmel |

| 文件页数: | 81/84页 |

| 文件大小: | 0K |

| 描述: | IC 8051 MCU ROMLESS 44PLCC |

| 标准包装: | 972 |

| 系列: | 80C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 30/20MHz |

| 连通性: | UART/USART |

| 外围设备: | POR,PWM,WDT |

| 输入/输出数: | 32 |

| 程序存储器类型: | ROMless |

| RAM 容量: | 512 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 5.5 V |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 44-LCC(J 形引线) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

DS70292G-page 84

2007-2012 Microchip Technology Inc.

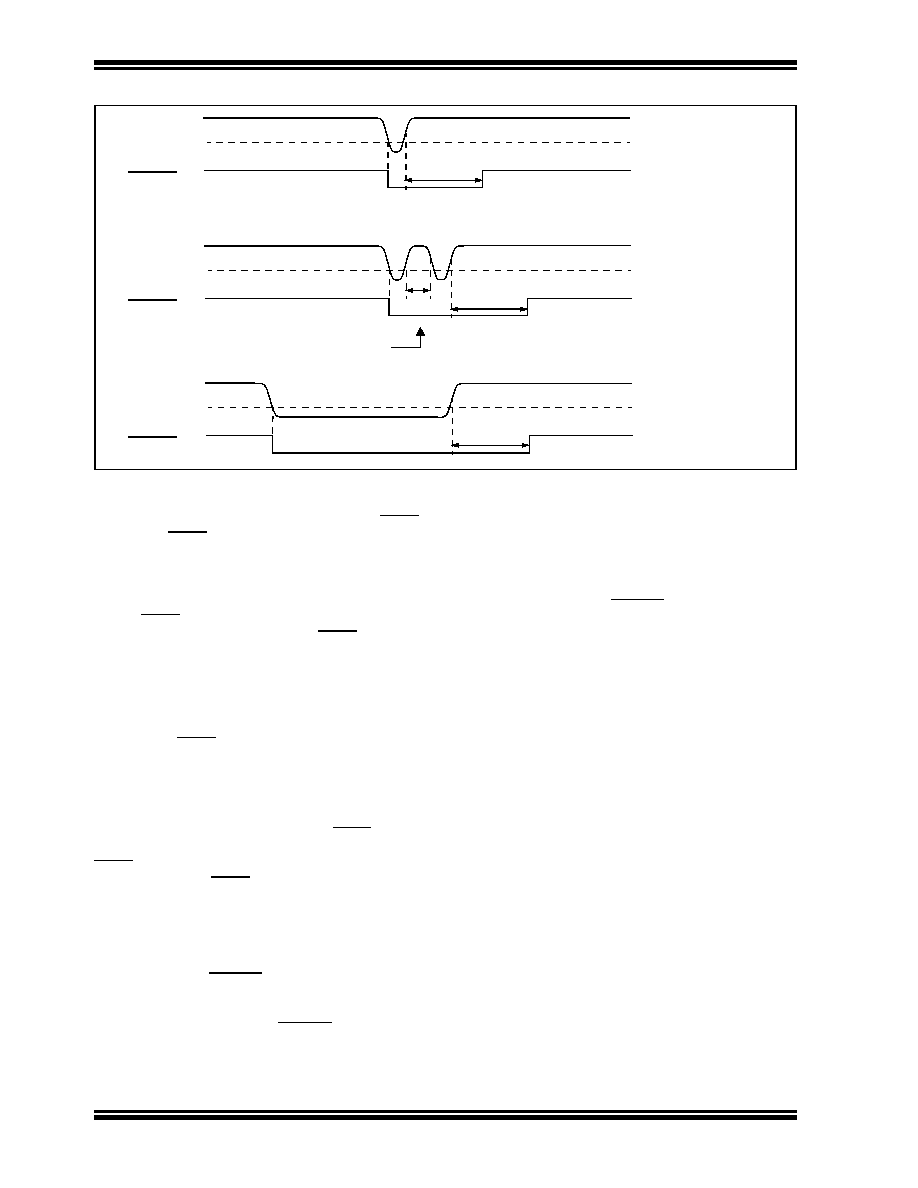

FIGURE 6-3:

BROWN-OUT SITUATIONS

6.5

External Reset (EXTR)

The external Reset is generated by driving the MCLR

pin low. The MCLR pin is a Schmitt trigger input with an

additional glitch filter. Reset pulses that are longer than

the minimum pulse-width will generate a Reset. Refer

minimum pulse-width specifications. The External

Reset (MCLR) Pin (EXTR) bit in the Reset Control

register (RCON) is set to indicate the MCLR Reset.

6.5.0.1

EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that

generate reset signals to Reset multiple devices in the

system. This external Reset signal can be directly con-

nected to the MCLR pin to Reset the device when the

rest of system is Reset.

6.5.0.2

INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to

Reset the device, the external reset pin (MCLR) should

be tied directly or resistively to VDD. In this case, the

MCLR pin will not be used to generate a Reset. The

external reset pin (MCLR) does not have an internal

pull-up and must not be left unconnected.

6.6

Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the

device will assert SYSRST, placing the device in a

special Reset state. This Reset state will not re-

initialize the clock. The clock source in effect prior to the

RESET instruction will remain. SYSRST is released at

the next instruction cycle, and the reset vector fetch will

commence.

The Software Reset (Instruction) Flag (SWR) bit in the

Reset Control (RCON<6>) register is set to indicate

the software Reset.

6.7

Watchdog Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will

asynchronously assert SYSRST. The clock source will

remain unchanged. A WDT time-out during Sleep or

Idle mode will wake-up the processor, but will not reset

the processor.

The Watchdog Timer Time-out Flag (WDTO) bit in the

Reset Control register (RCON<4>) is set to indicate

the

Watchdog

Reset.

Refer

to

“Watchdog Timer (WDT)” for more information on

Watchdog Reset.

6.8

Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-prior-

ity trap is being processed, a hard trap conflict Reset

occurs. The hard traps include exceptions of priority

level 13 through level 15, inclusive. The address error

(level 13) and oscillator error (level 14) traps fall into

this category.

The Trap Reset Flag (TRAPR) bit in the Reset Control

register (RCON<15>) is set to indicate the Trap Conflict

Reset. Refer to Section 7.0 “Interrupt Controller” for

more information on trap conflict Resets.

VDD

SYSRST

VBOR

VDD

SYSRST

VBOR

VDD

SYSRST

VBOR

TBOR + TPWRT

VDD dips before PWRT expires

TBOR + TPWRT

相关PDF资料 |

PDF描述 |

|---|---|

| AT80C51RA2-RLTUM | IC 8051 MCU ROMLESS 44VQFP |

| 213931-5 | CONN JACKSCREW RECEPT 34 POS |

| AT80C51RA2-RLTUL | IC 8051 MCU ROMLESS 44VQFP |

| AT80C51RA2-3CSUM | IC 8051 MCU ROMLESS 40DIP |

| AT80C51RA2-3CSUL | IC 8051 MCU ROMLESS 40DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT80C51RA2-SLSUM | 功能描述:8位微控制器 -MCU RLESS RA 40MHZ 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| AT80C51RB2-3CSCM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:80C51 High Performance ROM 8-bit Microcontroller |

| AT80C51RB2-3CSIM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:80C51 High Performance ROM 8-bit Microcontroller |

| AT80C51RB2-3CSUM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:80C51 High Performance ROM 8-bit Microcontroller |

| AT80C51RB2-RLTIL | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:80C51 High Performance ROM 8-bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。