- 您现在的位置:买卖IC网 > PDF目录12043 > AT89C51RD2-SLRUM (Atmel)IC MCU FLASH 8051 EEP 64K 44PLCC PDF资料下载

参数资料

| 型号: | AT89C51RD2-SLRUM |

| 厂商: | Atmel |

| 文件页数: | 99/137页 |

| 文件大小: | 0K |

| 描述: | IC MCU FLASH 8051 EEP 64K 44PLCC |

| 产品培训模块: | MCU Product Line Introduction |

| 标准包装: | 1 |

| 系列: | 89C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 60MHz |

| 连通性: | SPI,UART/USART |

| 外围设备: | POR,PWM,WDT |

| 输入/输出数: | 34 |

| 程序存储器容量: | 64KB(64K x 8) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 2K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 5.5 V |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 44-LCC(J 形引线) |

| 包装: | 标准包装 |

| 配用: | AT89OCD-01-ND - USB EMULATOR FOR AT8XC51 MCU AT89STK-11-ND - KIT STARTER FOR AT89C51RX2 |

| 其它名称: | AT89C51RD2-SLRUMDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页当前第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页

64

4235K–8051–05/08

AT89C51RD2/ED2

16.2.3

SPI Serial Clock (SCK)

This signal is used to synchronize the data movement both in and out of the devices through

their MOSI and MISO lines. It is driven by the Master for eight clock cycles which allows to

exchange one Byte on the serial lines.

16.2.4

Slave Select (SS)

Each Slave peripheral is selected by one Slave Select pin (SS). This signal must stay low for any

message for a Slave. It is obvious that only one Master (SS high level) can drive the network.

The Master may select each Slave device by software through port pins (Figure 16-2). To pre-

vent bus conflicts on the MISO line, only one slave should be selected at a time by the Master

for a transmission.

In a Master configuration, the SS line can be used in conjunction with the MODF flag in the SPI

Status register (SPSTA) to prevent multiple masters from driving MOSI and SCK (see Error

conditions).

A high level on the SS pin puts the MISO line of a Slave SPI in a high-impedance state.

The SS pin could be used as a general-purpose if the following conditions are met:

The device is configured as a Master and the SSDIS control bit in SPCON is set. This kind of

configuration can be found when only one Master is driving the network and there is no way

that the SS pin could be pulled low. Therefore, the MODF flag in the SPSTA will never be

set(1).

The Device is configured as a Slave with CPHA and SSDIS control bits set(2). This kind of

configuration can happen when the system comprises one Master and one Slave only.

Therefore, the device should always be selected and there is no reason that the Master uses

the SS pin to select the communicating Slave device.

Note:

1. Clearing SSDIS control bit does not clear MODF.

2. Special care should be taken not to set SSDIS control bit when CPHA = ’0’ because in this

mode, the SS is used to start the transmission.

16.2.5

Baud Rate

In Master mode, the baud rate can be selected from a baud rate generator which is controlled by

three bits in the SPCON register: SPR2, SPR1 and SPR0.The Master clock is selected from one

of seven clock rates resulting from the division of the internal clock by 2, 4, 8, 16, 32, 64 or 128.

Table 16-1 gives the different clock rates selected by SPR2:SPR1:SPR0.

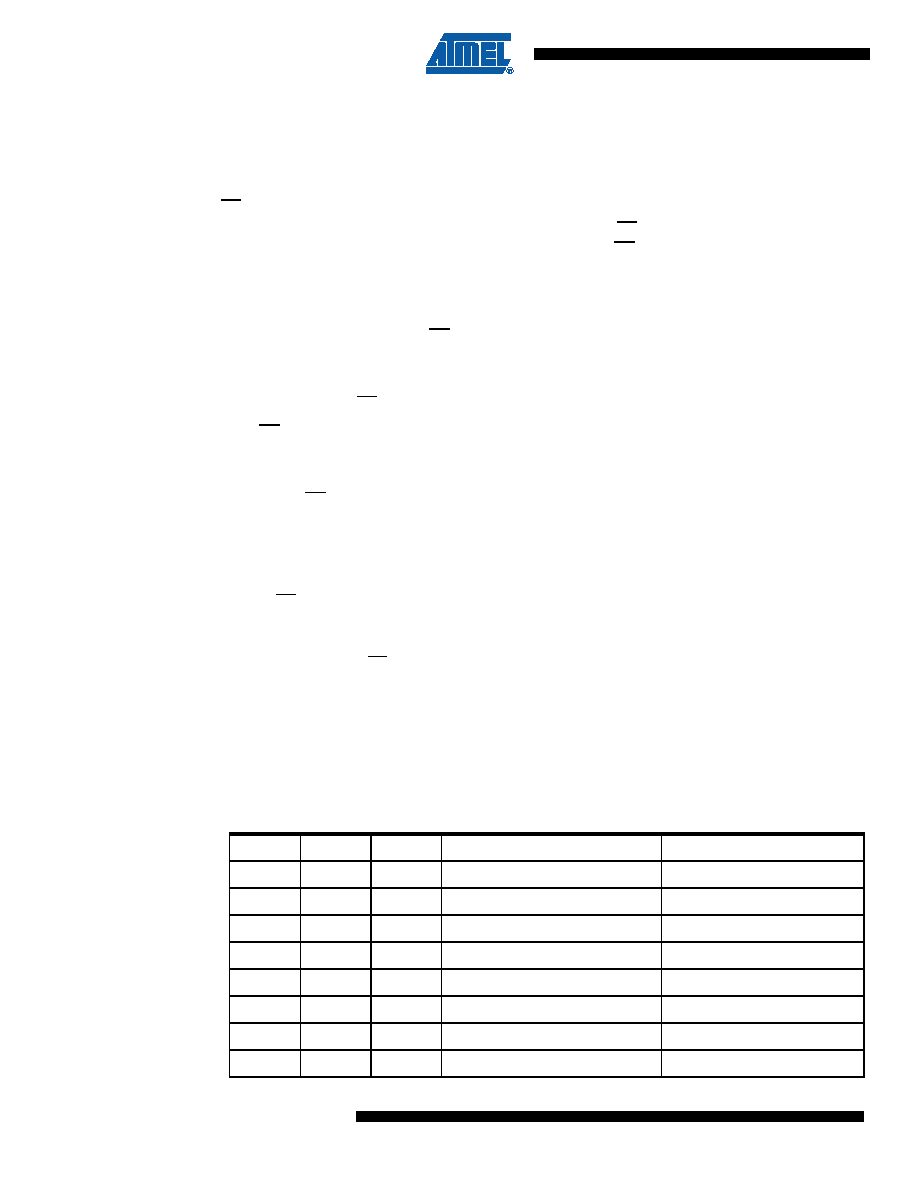

Table 16-1.

SPI Master Baud Rate Selection

SPR2

SPR1

SPR0

Clock Rate

Baud Rate Divisor (BD)

0

F

CLK PERIPH /2

2

0

1

F

CLK PERIPH /4

4

0

1

0

F

CLK PERIPH/8

8

0

1

F

CLK PERIPH /16

16

1

0

F

CLK PERIPH /32

32

1

0

1

F

CLK PERIPH /64

64

1

0

F

CLK PERIPH /128

128

1

Don’t Use

No BRG

相关PDF资料 |

PDF描述 |

|---|---|

| VE-23V-IY-F2 | CONVERTER MOD DC/DC 5.8V 50W |

| VE-23V-IY-F1 | CONVERTER MOD DC/DC 5.8V 50W |

| D-621-0424 | CONN JACK TRIAXIAL W/SOCKET |

| 5221629-6 | CONN TERMINATR PLUG BNC 93OHM AU |

| VE-23T-IY-F2 | CONVERTER MOD DC/DC 6.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT89C51RD2-SLSIM | 功能描述:IC 8051 MCU FLASH 64K 44PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:89C 标准包装:9 系列:87C 核心处理器:8051 芯体尺寸:8-位 速度:40/20MHz 连通性:UART/USART 外围设备:POR,WDT 输入/输出数:32 程序存储器容量:32KB(32K x 8) 程序存储器类型:OTP EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:- 振荡器型:内部 工作温度:0°C ~ 70°C 封装/外壳:40-DIP(0.600",15.24mm) 包装:管件 |

| AT89C51RD2-SLSUM | 功能描述:8位微控制器 -MCU 64kB Flash 2048B RAM 2.7V-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| AT89C51RD2-SLSUM | 制造商:Atmel Corporation 功能描述:IC 8BIT MCU C51/C251 60MHZ 44-PLCC |

| AT89C51RD2-SMSIM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Flash Microcontroller |

| AT89C51RD2-SMSUM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Flash Microcontroller |

发布紧急采购,3分钟左右您将得到回复。