参数资料

| 型号: | BR24L16-W |

| 厂商: | Rohm Semiconductor |

| 文件页数: | 32/41页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 16KBIT 400KHZ 8DIP |

| 标准包装: | 2,000 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 16K (2K x 8) |

| 速度: | 400kHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-DIP |

| 包装: | 管件 |

| 产品目录页面: | 1379 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

�� �

�

BR24L� □□� -W� Series,BR24S� □□□� -W� Series�

�Technical� Note�

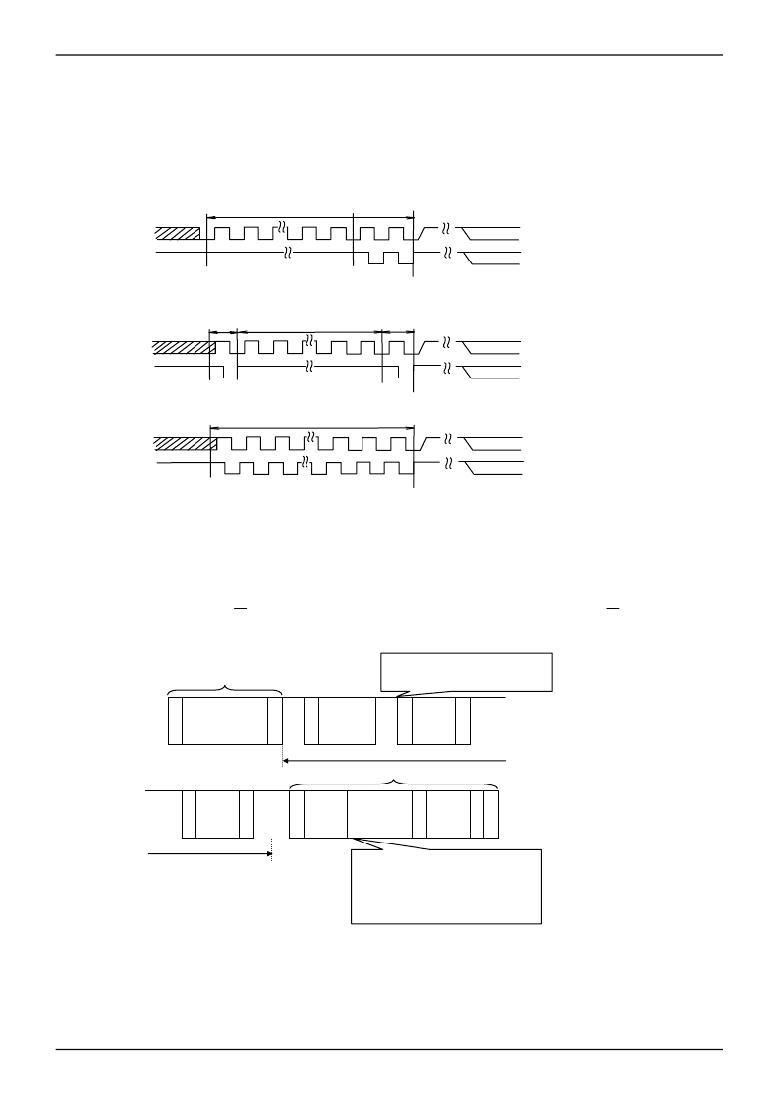

�●� Software� reset�

�Software� reset� is� executed� when� to� avoid� malfunction� after� power� on,� and� to� reset� during� command� input.� Software� reset�

�has� several� kinds,� and� 3� kids� of� them� are� shown� in� the� figure� below.� (Refer� to� Fig.45(a),� Fig.45(b),� Fig.45(c).)� In� dummy�

�clock� input� area,� release� the� SDA� bus� ('H'� by� pull� up).� In� dummy� clock� area,� ACK� output� and� read� data� '0'� (both� 'L'� level)� may�

�be� output� from� EEPROM,� therefore,� if� 'H'� is� input� forcibly,� output� may� conflict� and� over� current� may� flow,� leading� to�

�instantaneous� power� failure� of� system� power� source� or� influence� upon� devices.�

�Dummy� clock×14�

�Start×2�

�SCL�

�1�

�2�

�13�

�14�

�Normal� command�

�SDA�

�Normal� command�

�Fig.45-(a)� The� case� of� 14� Dummy� clock� +� START� +� START+� command� input�

�Start�

�Dummy� clock×9�

�Start�

�SCL�

�1�

�2�

�8�

�9�

�Normal� command�

�SDA�

�Normal� command�

�Fig.45-(b)� The� case� of� START+9� Dummy� clock� +� START� +� command� input�

�Start×9�

�SCL�

�1�

�2�

�3�

�7�

�8�

�9�

�Normal� command�

�SDA�

�Normal� command�

�*� Start� command� from� START� input.�

�Fig.45-(c)� START� � 9� +� command� input�

�●� Acknowledge� polling�

�During� internal� write,� all� input� commands� are� ignored,� therefore� ACK� is� not� sent� back.� During� internal� automatic� write�

�execution� after� write� cycle� input,� next� command� (slave� address)� is� sent,� and� if� the� first� ACK� signal� sends� back� 'L',� then� it�

�means� end� of� write� action,� while� if� it� sends� back� 'H',� it� means� now� in� writing.� By� use� of� acknowledge� polling,� next� command�

�can� be� executed� without� waiting� for� tWR� =� 5ms.�

�When� to� write� continuously,� R/W� =� 0,� when� to� carry� out� current� read� cycle� after� write,� slave� address� R/W� =� 1� is� sent,� and� if�

�ACK� signal� sends� back� 'L',� then� execute� word� address� input� and� data� so� forth.�

�First� write� command�

�During� internal� write,�

�ACK� =� HIGH� is� sent� back.�

�S�

�T�

�A�

�R�

�T�

�Write� command�

�S�

�T�

�O�

�P�

�S�

�T�

�A�

�R�

�T�

�Slave�

�address�

�A�

�C�

�K�

�H�

�S�

�T�

�A� Slave�

�R� address�

�T�

�A�

�C�

�K�

�H�

�…�

�t� WR�

�Second� write� command�

�…�

�S�

�T� Slave�

�A�

�R� address�

�T�

�A�

�C�

�K�

�H�

�S�

�T� Slave�

�A�

�R� address�

�T�

�A�

�C�

�K�

�L�

�Word�

�address�

�A�

�C�

�K�

�L�

�Data�

�A�

�C�

�K�

�L�

�S�

�T�

�O�

�P�

�t� WR�

�After� completion� of� internal�

�write,� ACK=LOW� is� sent� back,�

�so� input� next� word� address� and�

�data� in� succession.�

�Fig.46� Case� to� continuously� write� by� acknowledge� polling�

�www.rohm.com�

�?� 2009� ROHM� Co.,� Ltd.� All� rights� reserved.�

�32/40�

�2009.09� -� Rev.D�

�相关PDF资料 |

PDF描述 |

|---|---|

| AGLN250V2-VQ100I | IC FPGA NANO 1KB 250K 100VQFP |

| AGLN250V2-ZVQ100I | IC FPGA NANO 1KB 250K 100VQFP |

| EP1K10QC208-1N | IC ACEX 1K FPGA 10K 208-PQFP |

| EP1K10QC208-1 | IC ACEX 1K FPGA 10K 208-PQFP |

| BR25S256FJ-WE2 | IC EEPROM SPI 256KB 20MHZ 8-SOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BR24L256FJ-WE2 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24L256FJ-WTR | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24L256FVJ-WE2 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24L256FVJ-WTR | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24L256FVM-WE2 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

发布紧急采购,3分钟左右您将得到回复。