- 您现在的位置:买卖IC网 > PDF目录4520 > BR25S128FV-WE2 (Rohm Semiconductor)IC EEPROM SPI 128KB 20MHZ 8-SSOP PDF资料下载

参数资料

| 型号: | BR25S128FV-WE2 |

| 厂商: | Rohm Semiconductor |

| 文件页数: | 11/19页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM SPI 128KB 20MHZ 8-SSOP |

| 标准包装: | 1 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 128K (16K x 8) |

| 速度: | 20MHz |

| 接口: | SPI 3 线串行 |

| 电源电压: | 1.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-LSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-SSOPB |

| 包装: | 标准包装 |

| 其它名称: | BR25S128FV-WE2DKR |

�� �

�

BR25S� □□□� Series�

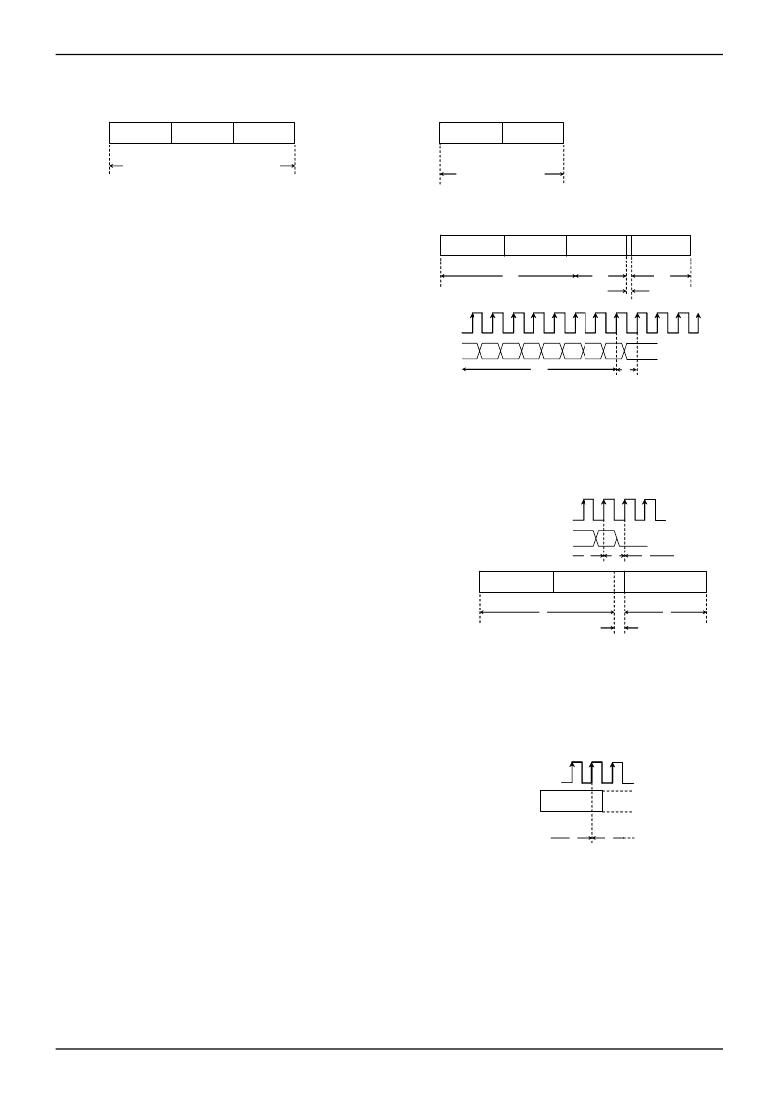

�●� Method� to� cancel� each� command�

�○� READ,� RDSR�

�?� Method� to� cancel� :� cancel� by� CSB� =� “H”.�

�Technical� Note�

�Ope� code�

�8� bits�

�Address�

�16� bits�

�Data�

�8� bits�

�Ope� code�

�8� bits�

�Data�

�8� bits�

�Cancel� available� in� all� areas� of� read� mode�

�Fig.40� READ� cancel� valid� timing�

�Cancel� available� in� all�

�areas� of� rdsr� mode�

�Fig.41� RDSR� cancel� valid� timing�

�○� WRITE� 、� PAGE� WRITE�

�a� :� Ope� code� or� address� input� area�

�Cancellation� is� available� by� CSB=”H”.�

�b� :� Data� input� area� (D7� ~� D1� input� area)�

�Ope� code�

�8bits�

�a�

�Address�

�16bits�

�Data�

�8bits�

�b�

�tE/W�

�d�

�Cancellation� is� available� by� CSB=”H”.�

�c� :� Data� input� area� (D0� area)�

�In� this� area,� cancellation� is� not� available.�

�When� CSB� is� set� HIGH,� write� starts.�

�SCK�

�c�

�d� :� tE/W� area�

�SI�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�In� the� area� c,� by� rising� CSB,� write� starts.�

�b�

�c�

�While� writing,� by� any� input,� cancellation� cannot� be� made.�

�Fig.42� WRITE� cancel� valid� timing�

�Note1)� If� Vcc� is� made� OFF� during� write� execution,� designated� address� data� is� not� guaranteed,� therefore� write� it� once� again.�

�Note2)� If� CSB� is� rised� at� the� same� timing� as� that� of� the� SCK� rise,� write� execution� /� cancel� becomes� unstable,� therefore,� it� is�

�recommended� to� rise� in� SCK� =� “L”� area.� As� for� SCK� rise,� assure� timing� of� tCSS� /� tCSH� or� more.�

�○� WRSR�

�a� :� From� ope� code� to� 15-th� clock� rise�

�SCK�

�14�

�15�

�16�

�17�

�Cancellation� is� available� by� CSB=”H”.�

�b� :� From� 15-th� clock� rise� to� 16-th� clock� rise� (write� enable� area)�

�SI�

�D1�

�D0�

�In� this� area,� cancellation� is� not� available.�

�a�

�b�

�c�

�When� CSB� is� set� HIGH,� write� starts.�

�c� :� After� 16-th� clock� rise.�

�Ope� code�

�Data�

�tE/W�

�Cancellation� is� available� by� CSB=”H”.�

�However,� if� write� starts� (CSB� is� rised)�

�8� bits�

�a�

�8� bits�

�c�

�in� the� area� b,� cancellation� cannot� be� made� by� any� means.�

�And,� by� inputting� on� SCK� clock,� cancellation� cannot� be� made.�

�b�

�Fig.43� WRSR� cancel� valid� timing�

�Note1)� If� Vcc� is� made� OFF� during� write� execution,� designated� address� data� is� not� guaranteed,� therefore� write� it� once�

�again�

�Note2)� If� CSB� is� rised� at� the� same� timing� as� that� of� the� SCK� rise,� write� execution� /� cancel� becomes� unstable,� therefore,� it�

�is� recommended� to� rise� in� SCK� =� “L”� area.� As� for� SCK� rise,� assure� timing� of� tCSS� /� tCSH� or� more.�

�○� WREN/WRDI�

�SCK�

�6�

�7�

�8�

�a� :� From� ope� code� to� 7-th� clock� rise,� cancellation� is� available� by� CSB� =� “H”.�

�b� :� Cancellation� is� not� available� 7-th� clock.�

�Ope� code�

�8� bits�

�a�

�b�

�Fig.44� WREN/WRDI� cancel� valid� timing�

�www.rohm.com�

�?� 2010� ROHM� Co.,� Ltd.� All� rights� reserved.�

�11/18�

�2010.12� -� Rev.B�

�相关PDF资料 |

PDF描述 |

|---|---|

| EX64-PTQ100I | IC FPGA ANTIFUSE 3K 100-TQFP |

| EX64-PTQG100I | IC FPGA ANTIFUSE 3K 100-TQFP |

| EP4CE10E22C9L | IC CYCLONE IV FPGA 10K 144EQFP |

| EP4CE10E22C8 | IC CYCLONE IV FPGA 10K 144EQFP |

| BR25S128FVT-WE2 | IC EEPROM SPI 128KB 20MHZ 8TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BR25S128F-WE2 | 功能描述:IC EEPROM SPI 128KB 20MHZ 8-SOP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:16K (1K x 16) 速度:2MHz 接口:Microwire 3 线串行 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOP-J 包装:Digi-Reel® 产品目录页面:1380 (CN2011-ZH PDF) 其它名称:BR93L86FJ-WE2DKR |

| BR25S128GUZ-W | 制造商:ROHM 制造商全称:Rohm 功能描述:WL-CSP EEPROMs family SPI BUS |

| BR25S128GUZ-W_11 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series Serial EEPROM Series WL-CSP EEPROMs family |

| BR25S128GUZ-WE2 | 功能描述:IC EEPROM SPI 128KB 12-WLCSP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:4G(256M x 16) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP I 包装:Digi-Reel® 其它名称:557-1461-6 |

| BR25S128-W | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series Serial EEPROMs |

发布紧急采购,3分钟左右您将得到回复。