- 您现在的位置:买卖IC网 > PDF目录236588 > BU-61559D1-100Q (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 PDF资料下载

参数资料

| 型号: | BU-61559D1-100Q |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| 封装: | 45.70 X 53.30 MM, 5.30 MM HEIGHT, CERAMIC, DDIP-78 |

| 文件页数: | 10/32页 |

| 文件大小: | 438K |

| 代理商: | BU-61559D1-100Q |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

18

Data Device Corporation

www.ddc-web.com

BU-61559 Series

E-03/06-0

BUFFERED MODE

In the buffered mode (reference FIGURE 19), the processor data

and address buses connect directly to the corresponding buses

of the BU-61559. In this mode, the shared memory size is limit-

ed to the 8K X 16 of internal RAM. In the buffered mode, the

internal address latches and data buffers serve to isolate the

external processor address/data buses from the internal memo-

ry address/data buses.

The BU-61559 supports a direct interface to a multiplexed

processor bus by means of the input signal ADDR_LAT. When

ADDR_LAT is high, the latch/buffers for A15-A0 are in their trans-

parent mode. When ADDR_LAT is low, the latch/buffers for A15-

A0 are in their latched mode. In the buffered mode, the address

latch/buffers are directed inward for CPU accesses and are dis-

abled for 1553 accesses. The bidirectional data buffers are

directed inward for CPU write transfers, outward for CPU read

transfers, and are disabled for 1553 transfers.

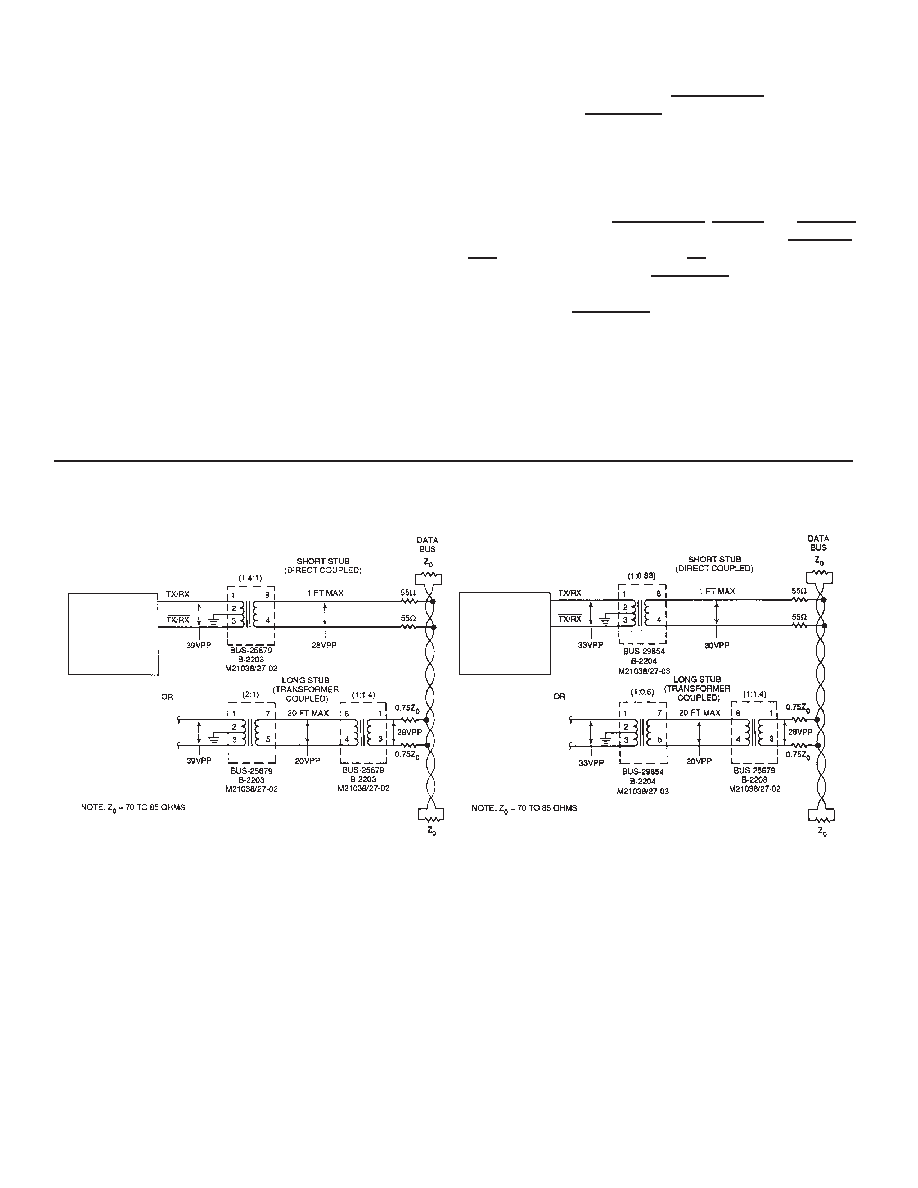

FIGURE 18. BU-61559X1, BU-61559X2 INTERFACE TO 1553 BUS

NOTES for FIGURE 18:

(1) Shown for one of two redundant buses that interface to the BU-61559/60 Series hybrid.

(2) Transmitted voltage level on 1553 bus is 6 Vp-p min, 7 Vp-p nominal, 9 Vp-p max.

(3) Required tolerance on isolation resistors is 2%. Instantaneous power dissipation (when transmitting) is approximately 0.5 W (typ), 0.8 W (max).

(4) Transformer pin numbering is correct for DDC BUS-25679 or BUS-29854 transformer. For the Beta transformer (e.g., B-2203) or the QPL-21038-31 transformer (e.g.,

M21038/27-02), the winding sense and turns ratio are mechanically the same, but the pin numbering is reversed. Therefore, it is necessary to reverse pins 8 and 4 or

pins 7 and 5 in the diagram for the Beta or QPL transformers.

In the buffered mode, the output MEMENA-OUT must be con-

nected to the input MEMENA-IN.

TRANSPARENT MODE

The transparent mode (reference FIGURE 20) supports an inter-

face to up to 64K words of external shared RAM and/or to a

STANAG-3910 component set. In the transparent mode, the

memory control signals MEMENA-OUT, MEMOE, and MEMWR

are used to read and write data from/to external RAM. MEMENA-

OUT is the BU-61559's Chip Select (CS) output signal. For inter-

nal RAM accesses, the input MEMENA-IN should be asserted

low. When there is no ongoing memory access, or for accesses

to external RAM, MEMENA-IN should be presented as a logic 1.

In the transparent mode, the address buffers drive the CPU

address onto the internal memory bus for CPU transfers; for

1553 transfers, the internal memory address is asserted on the

external address bus. The data buffers are directed outward for

BU-61559X1

BU-61559X2

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61559D1-120Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-150K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-440 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-480K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-820S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553 Components |ACE |

| BU-61580G1-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。