- 您现在的位置:买卖IC网 > PDF目录236588 > BU-61559D1-100Q (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 PDF资料下载

参数资料

| 型号: | BU-61559D1-100Q |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| 封装: | 45.70 X 53.30 MM, 5.30 MM HEIGHT, CERAMIC, DDIP-78 |

| 文件页数: | 4/32页 |

| 文件大小: | 438K |

| 代理商: | BU-61559D1-100Q |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

12

Data Device Corporation

www.ddc-web.com

BU-61559 Series

E-03/06-0

Words are used to specify the RT memory management scheme

for each Tx/Rx/Bcst-subaddresses. If used, address range 0300-

03FF is dedicated as the illegalizing section of RAM. The actual

Stack RAM area as well as the individual data blocks may be

located in any of the non-fixed areas in the shared RAM address

space.

TABLE 3A illustrates the RT memory map for the case where the

internal illegalizing feature is used. By connecting the ILLENA

input to logic 1 (+5V), address locations 0300-03FF (hex) are

dedicated for the command illegalizing function. TABLE 3B illus-

trates the typical memory map for the case when the internal ille-

galization feature is not used. In this instance, ILLENA must be

strapped to logic 0 (ground) so that address locations 0300-03FF

(hex) may be used for storage of stack data or message data

blocks.

ACTIVE AREA DOUBLE BUFFERING

The BU-61559 provides a global double buffering mechanism by

means of bit 13, CURRENT AREA B/A, of Configuration

Register #1. At any point in time, this allows for one stack point-

er, stack area, Lookup Table, and set of data blocks to be desig-

nated as “active” (used for the processing of 1553 messages)

and the alternate set of respective data structures to be desig-

nated as “non-active”. Both the “active” and “non-active” RAM

areas are always accessible by the host processor.

RT LOOKUP TABLES

Referring to TABLE 4, the RT Lookup tables are expanded

beyond those of the BUS-61553. In the 61553, the Lookup

Tables are 64 words each, containing the Lookup Table pointers

for the 32 receive subaddresses and the 32 transmit subad-

dresses. For the BU-61559, there are an additional 64 words in

Subaddress

Control Word

Lookup Table

(Optional)

SACW SA0

SACW SA31

0220

023F

01A0

01BF

Broadcast

Lookup Table

(Optional)

Bcst SA0

Bcst SA31

0200

021F

0180

019F

Transmit

Lookup Table

Tx SA0

Tx SA31

01E0

01FF

0160

017F

Receive

(/Broadcast)

Lookup Table

Rx(/Bcst) SA0

Rx(/Bcst) SA31

01C0

01DF

0140

015F

COMMENT

DESCRIPTION

AREA B

AREA A

TABLE 4. RT LOOK-UP TABLES

each of the two Lookup Tables. Thirty two (32) of these words

provide optional separation of broadcast messages. The last 32

words are subaddress control words, one appropriated for each

RT subaddress.

SUBADDRESS CONTROL WORD

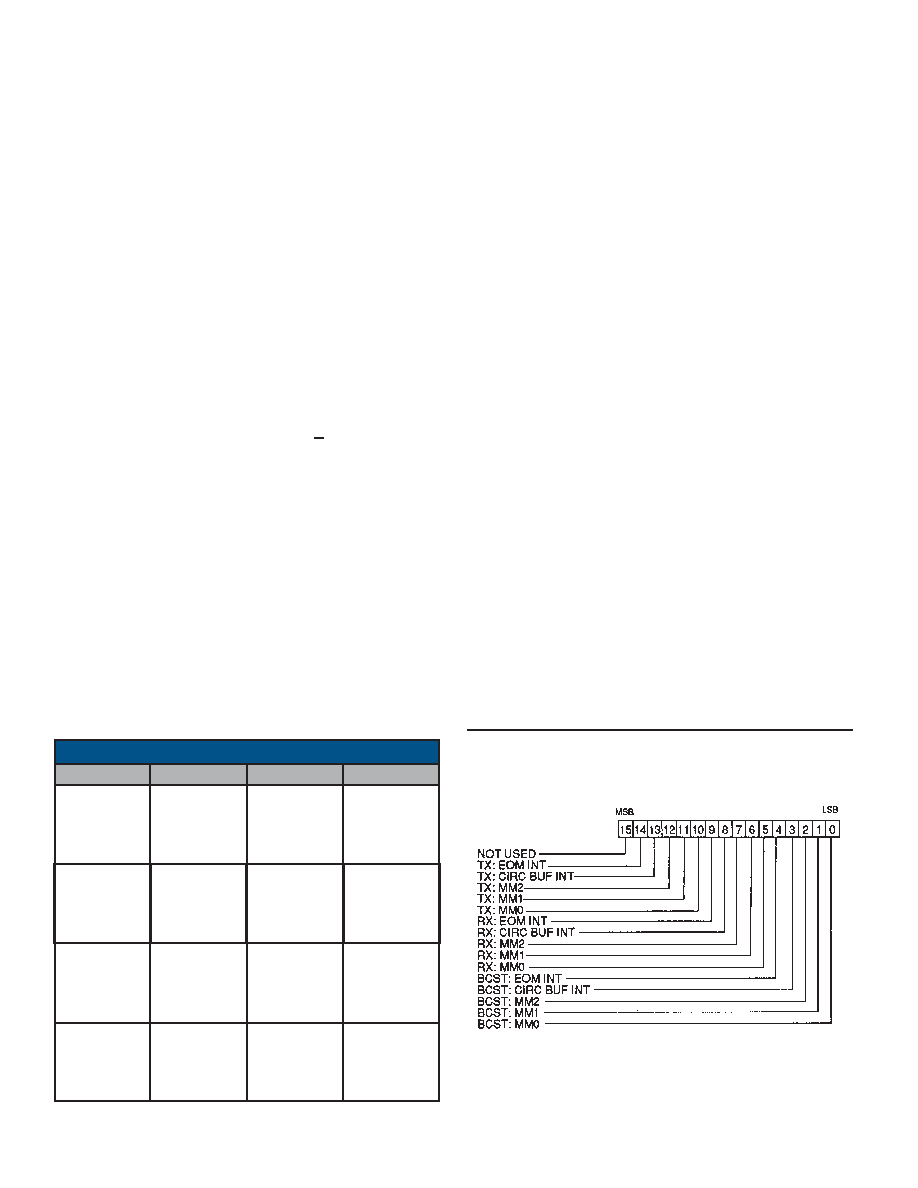

Referring to FIGURE 13.1 and TABLE 5, in the Enhanced RT

Memory Management mode, each of the 32 Subaddress Control

Words specifies the memory management and interrupt

schemes for the respective subaddress. For each Subaddress

Control Word, five bits control the memory management scheme

and interrupts for each of transmit, receive, and broadcast mes-

sages.

For each transmit, receive, or broadcast subaddress, three bits

are used to specify the memory management scheme. For each

Tx/Rx/Bcst subaddress, the memory management scheme may

be selected for either the “single message” mode or the “circular

buffer” mode.

In the single message mode, a single data block is repeatedly

overread (for transmit data) or overwritten (for receive or broad-

cast data). Alternatively, in the circular buffer mode, Data Words

for successive messages to/from any particular Tx/Rx/Bcst sub-

addresses are read from or written to the next contiguous block

of locations in the respective circular buffer.

The size of the circular buffer for each transmit, receive, or

broadcast subaddress may be programmed for 128, 256, 512,

1024, 2048, 4096, or 8192 words. For each Tx/Rx/Bcst subad-

dress, two bits of the subaddress control word are used to

enable interrupts. One of these bits will result in an interrupt fol-

lowing every message directed to the specific Tx/Rx/Bcst sub-

FIGURE 13.1 SUBADDRESS CONTROL WORD BIT

MAP

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61559D1-120Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-150K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-440 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-480K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-820S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553 Components |ACE |

| BU-61580G1-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。