- 您现在的位置:买卖IC网 > PDF目录223464 > BU-64703B4-300 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CBGA80 PDF资料下载

参数资料

| 型号: | BU-64703B4-300 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CBGA80 |

| 封装: | CERAMIC, BGA-80 |

| 文件页数: | 36/48页 |

| 文件大小: | 405K |

| 代理商: | BU-64703B4-300 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

41

Data Device Corporation

www.ddc-web.com

BU-64703

D-03/06-0

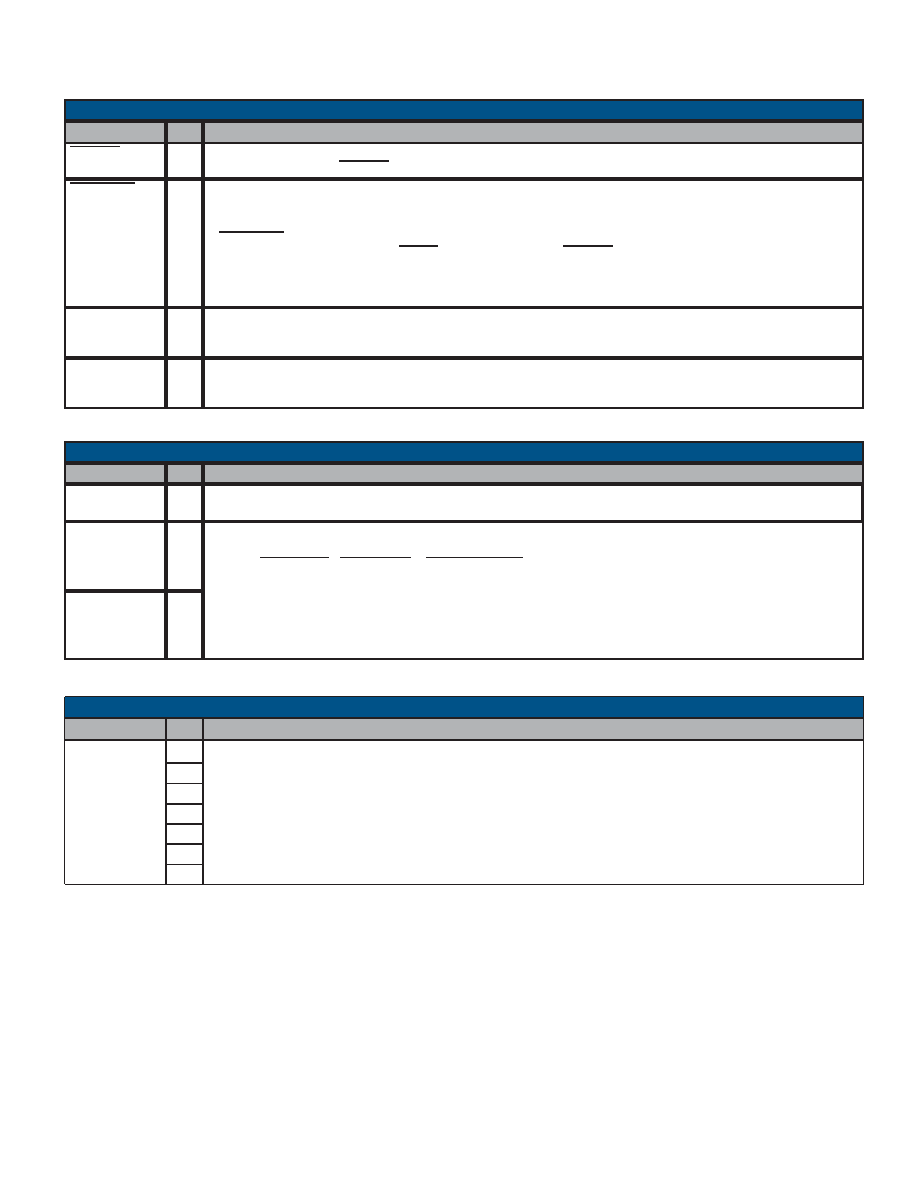

DESCRIPTION

Transmitter inhibit input for the MIL-STD-1553 transmitters. For normal operation, this input should be connected to logic

"0". To force a shutdown of the Channel A and Channel B transmitters, a value of logic "1" should be applied to this input.

TX_INH (I)

65

Broadcast Enable. If this input is logic "1", the SSRT Mark3 will recognize RT address 31 as the broadcast address. If this

input is logic "0", the SSRT Mark3 will not recognize RT address 31 as the broadcast address; however, in this configura-

tion, RT address 31 may be used as a standard RT address.

BRO_ENA (I)

71

Auto-configure input. If connected to logic "1", then the auto-configure option is disabled, and the six configuration para-

meters revert to their default values as listed in TABLE 2. Note that the default condition for each configuration parameter

is enabled (for the MIL-STD-1553A/B protocol selection, -1553B is the default).

If AUTO_CFG is connected to logic "0", then the configuration parameters are transferred over D5-D0 during a DMA read

data transfer, when RTACTIVE and DTACK are logic "0", following MSTCLR transitioning from logic "0" to logic "1". Each

of the configuration parameters is enabled if the SSRT Mark3 reads a value of logic "1" for the respective data bit.

AUTO_CFG (I)

76

Master Clear. Negative true Reset input, asserted low following power turn-on. When coming out of a “reset” condition,

note that the risetime of MSTCLR must be less than 10 s.

MSTCLR (I)

25

SIGNAL

TABLE 15. CONTROL INPUTS

PIN

DESCRIPTION

SIGNAL

TABLE 16. CLOCK INPUT

Clock Input. The clock frequency must be designated by means of the CLK_SEL_1 and CLK_SEL_0 inputs.

CLK_IN (I)

26

PIN

These two inputs are used to designate the SSRT Mark3's clock frequency, as follows:

CLK_SEL_1

CLK_SEL_0

Clock Frequency

0

10 MHz

0

1

20 MHz

1

0

12 MHz

1

16 MHz

CLK_SEL_1 (I)

73

CLK_SEL_0 (I)

80

DESCRIPTION

SIGNAL

TABLE 17. FACTORY TEST (NO USER CONNECTIONS)

NC

4

PIN

For factory test only. Do not connect for normal operation.

8

9

16

11

21

23

相关PDF资料 |

PDF描述 |

|---|---|

| BU-64703B9-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CBGA80 |

| BU-65551M2-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, XMA68 |

| BU-65550M1-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, XMA68 |

| BU-66318G0-110 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PQFP208 |

| BU2294AF | 67.735842 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-65-0 | 功能描述:测试电夹 ALLIGATOR CLIP BLK RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU65-0 | 制造商:MUELLER ELECTRIC CO. 功能描述: 制造商:Mueller Electric Company 功能描述: |

| BU-651-0 | 功能描述:测试电夹 Black Shrouded Small RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU-651-2 | 功能描述:测试电夹 Red Shrouded Small A RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU65170G0-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Interface IC |

发布紧急采购,3分钟左右您将得到回复。