- 您现在的位置:买卖IC网 > PDF目录166631 > BU-65743F3-300 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF资料下载

参数资料

| 型号: | BU-65743F3-300 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封装: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件页数: | 21/75页 |

| 文件大小: | 532K |

| 代理商: | BU-65743F3-300 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

28

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

8

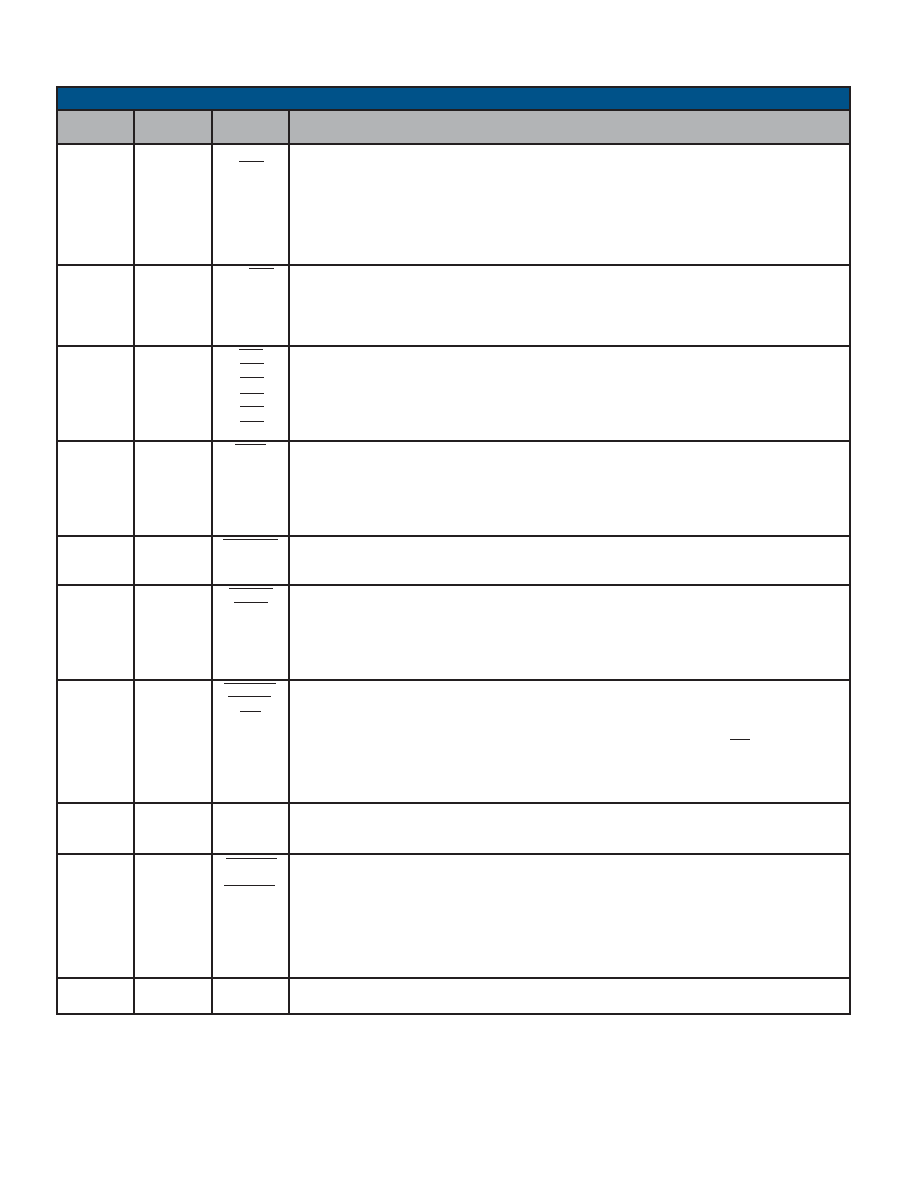

TABLE 53. CONDITION CODES

BIT

CODE

LT/GP0

EQ/GP1

RETRY0

RETRY1

RETRY0

RETRY1

D

E

GP2

GP3

GP4

GP5

GP6

GP7

NORESP

GD BLK

XFER

NAME

(BIT 4 = 0)

These two bits reflect the retry status of the most recent message. The number of times that the mes-

sage was retried is delineated by these two bits as shown below:

RETRY COUNT 1

RETRY COUNT 0

Number of

(bit 14)

(bit 13)

Message Retries

0

1

0

N/A

1

2

FUNCTIONAL DESCRIPTION

INVERSE

(BIT 4 = 1)

GT/

GP0

NE/GP1

0

ALWAYS

Less Than Flag set or cleared after CFT or CMT operation. Also, General Purpose Flag 0 may be set

or cleared by a FLG operation.

NEVER

F

GP2

GP3

GP4

GP5

GP6

GP7

1

RESP

Equal Flag set or cleared after CFT or CMT operation. Also, General Purpose Flag 1 may also be set

or cleared by a FLG operation.

GD BLK

XFER

BAD

MESSAGE

GOOD

MESSAGE

The ALWAYS bit should be set (bit 4 = 0) to designate an instruction as unconditional. The NEVER bit

(bit 4 =1) can be used to implement an NOP instruction.

C

BAD MESSAGE indicates either a format error, loop test fail, or no response error for the most recent

message. Note that a "Status Set" condition has no effect on the "BAD MESSAGE/GOOD MESSAGE"

condition code.

FMT ERR

9

FMT ERR indicates that the received portion of the most recent message contained one or more viola-

tions of the 1553 message validation criteria (sync, encoding, parity, bit count, word count, etc.), or the

RT's status word received from a responding RT contained an incorrect RT address field.

MASKED

STATUS

BIT

MASKED

STATUS

BIT

B

General Purpose Flags may be set, cleared, or toggled by a FLG operation. The host processor can

set, clear, or toggle these flags in the same way as the FLG instruction by means of the BC GENERAL

PURPOSE FLAG REGISTER.

Indicates that one or both of the following conditions have occurred for the most recent message: (1) If

one (or more) of the Status Mask bits (14 through 9) in the BC Control Word is logic "0" and the corre-

sponding bit(s) is (are) set (logic "1") in the received RT Status Word. In the case of the RESERVED

BITS MASK (bit 9) set to logic "0", any or all of the 3 Reserved Status Word bits being set will result in

a MASKED STATUS SET condition; and/or (2) If BROADCAST MASK ENABLED/XOR (bit 11 of

Configuration Register #4) is logic "1" and the MASK BROADCAST bit of the message's BC Control

Word is logic "0" and the BROADCAST COMMAND RECEIVED bit in the received RT Status Word is

logic "1".

2

3

4

5

6

7

NORESP indicates that an RT has either not responded or has responded later than the BC No

Response Timeout time. The PCI Mini-ACE Mark3/Micro-ACE TE's No Response Timeout Time is

defined per MIL-STD-1553B as the time from the mid-bit crossing of the parity bit to the mid-sync cross-

ing of the RT Status Word. The value of the No Response Timeout value is programmable from among

the nominal values 18.5, 22.5, 50.5, and 130 s (±1 s) by means of bits 10 and 9 of Configuration

Register #5.

A

For the most recent message, GD BLK XFER will be set to logic "1" following completion of a valid

(error-free) RT-to-BC transfer, RT-to-RT transfer, or transmit mode code with data message. This bit is

set to logic "0" following an invalid message. GOOD DATA BLOCK TRANSFER is always logic "0" fol-

lowing a BC-to-RT transfer, a mode code with data, or a mode code without data. The Loop Test has

no effect on GOOD DATA BLOCK TRANSFER. GOOD DATA BLOCK TRANSFER may be used to

determine if the transmitting portion of an RT-to-RT transfer was error free.

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65863F3-310 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65743F3-200 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65863F3-220 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65843B3-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65863B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU6574FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6574FV-E2 | 功能描述:IC ANALOG FRONT END SSOP20 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| BU6577FV | 制造商:ROHM 制造商全称:Rohm 功能描述:Silicon monolithic integrated circuit |

| BU6577FV-E2 | 制造商:ROHM Semiconductor 功能描述:ANALOG FRONT END - Tape and Reel |

| BU6581KV | 制造商:未知厂家 制造商全称:未知厂家 功能描述:コミュニケーションLSI |

发布紧急采购,3分钟左右您将得到回复。