- 您现在的位置:买卖IC网 > PDF目录298893 > BXM80526B600128 (INTEL CORP) 64-BIT, 600 MHz, MICROPROCESSOR, PBGA495 PDF资料下载

参数资料

| 型号: | BXM80526B600128 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, 600 MHz, MICROPROCESSOR, PBGA495 |

| 封装: | BGA2-495 |

| 文件页数: | 13/74页 |

| 文件大小: | 870K |

| 代理商: | BXM80526B600128 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

Mobile Intel Celeron Processor (0.18) in BGA2 and Micro-PGA2 Packages

at 700MHz, 650 MHz, 600 MHz, 550 MHz, 500 MHz, 450 MHz,

Low-voltage 500 MHz, and Low-voltage 400A MHz

Datasheet

Order#-XXX

13

The Open-drain output signals have open drain drivers and external pull-up resistors are required.

One of the two output signals (IERR#) is a catastrophic error indicator and is tri-stated (and

pulled-up) when the processor is functioning normally. The FERR# output can be either tri-stated

or driven to VSS when the processor is in a low-power state depending on the condition of the

floating point unit. Since this signal is a DC current path when it is driven to VSS, Intel

recommends that the software clears or masks any floating-point error condition before putting the

processor into the Deep Sleep state.

3.1.5.3

Other Signals

The system bus clock (BCLK) must be driven in all of the low-power states except the Deep Sleep

state. The APIC clock (PICCLK) must be driven whenever BCLK is driven unless the APIC is

hardware disabled or the processor is in the Sleep state. Otherwise, it is permitted to turn off

PICCLK by holding it at VSS. The system bus clock should be held at VSS when it is stopped in the

Deep Sleep state.

In the Auto Halt and Stop Grant states the APIC bus data signals (PICD[1:0]) may toggle due to

APIC bus messages. These signals are required to be tri-stated and pulled-up when the processor

is in the Quick Start, Sleep, or Deep Sleep states unless the APIC is hardware disabled.

3.2

Power Supply Requirements

3.2.1

Decoupling Recommendations

The amount of bulk decoupling required on the VCC and VCCT planes to meet the voltage tolerance

requirements for the mobile Celeron processor are a strong function of the power supply design.

Contact your Intel Field Sales Representative for tools to help determine how much bulk

decoupling is required. The processor core power plan (VCC) should have eight 0.1-F high

frequency decoupling capacitors placed underneath the die and twenty 0.1-

F mid frequency

decoupling capacitors placed around the die as close to the die as flex solution allows. The system

bus buffer power plane (VCCT) should have twenty 0.1-F high frequency decoupling capacitors

around the die.

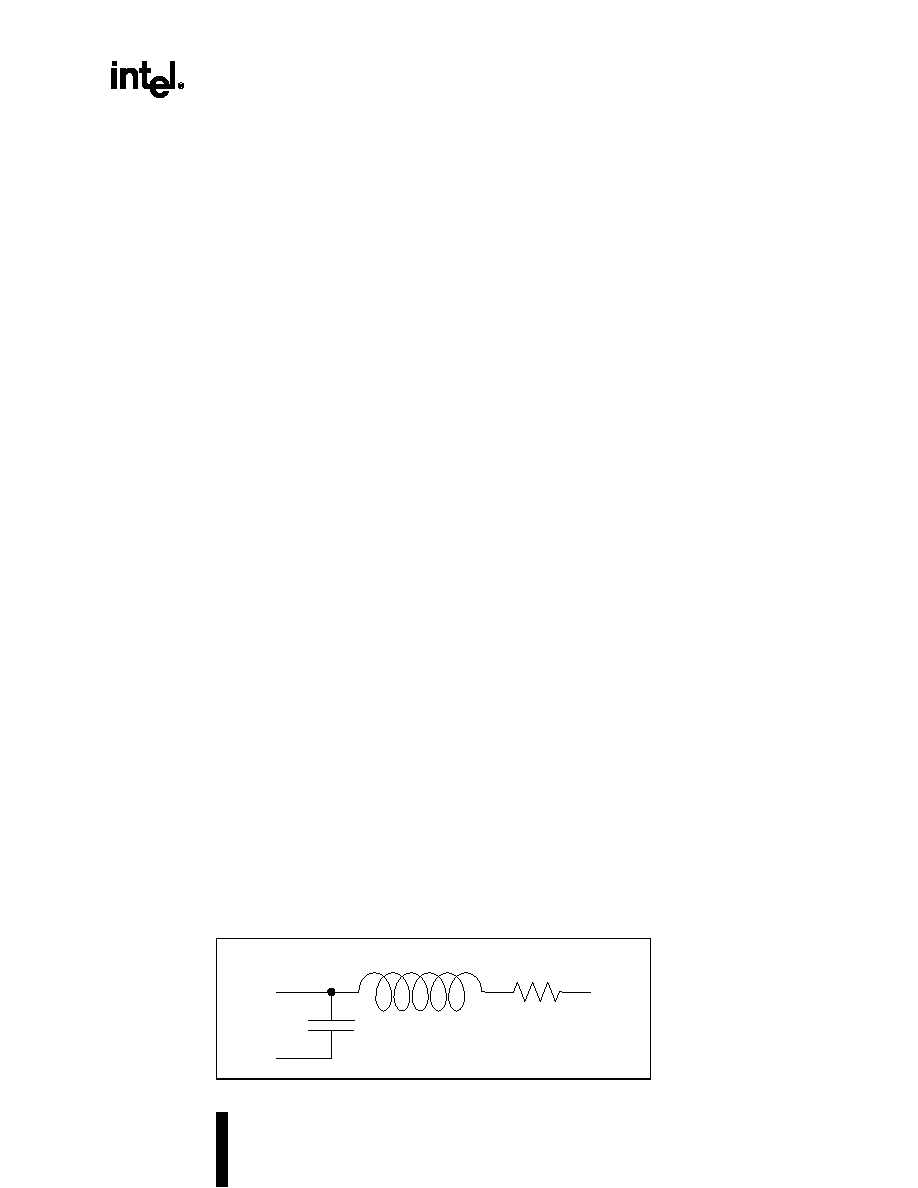

3.2.2

Voltage Planes

All VCC and VSS pins/balls must be connected to the appropriate voltage plane. All VCCT and VREF

pins/balls must be connected to the appropriate traces on the system electronics. In addition to the

main VCC, VCCT, and VSS power supply signals, PLL1 and PLL2 provide analog decoupling to the

PLL section. PLL1 and PLL2 should be connected according to Figure 4. Do not connect PLL2

directly to VSS. Appendix A contains the RLC filter specification.

Figure 4. PLL RLC Filter

PLL1

PLL2

V

CCT

V0027-01

L1

C1

R1

相关PDF资料 |

PDF描述 |

|---|---|

| BXM80526B700128 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80526B700 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80536GC2100F | 32-BIT, 2100 MHz, MICROPROCESSOR, CPGA478 |

| BXM80536GC1800F | 32-BIT, 1800 MHz, MICROPROCESSOR, CPGA478 |

| BXM80536GC1600F | 32-BIT, 1600 MHz, MICROPROCESSOR, CPGA478 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BXM80536NC1400ES L7LS | 制造商:Intel 功能描述:CELERON M,360,1.40GHZ,1M CACHE, 400MHZ FSB,1.26V,UFCPGA - Boxed Product (Development Kits) |

| BXMP1000 | 制造商:SPECTRUM 制造商全称:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| BXMP1001 | 制造商:SPECTRUM 制造商全称:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| BXMP1002 | 制造商:SPECTRUM 制造商全称:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| BXMP1003 | 制造商:SPECTRUM 制造商全称:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

发布紧急采购,3分钟左右您将得到回复。