- 您现在的位置:买卖IC网 > PDF目录366628 > C9812DYB Up to 5A ULDO linear regulator PDF资料下载

参数资料

| 型号: | C9812DYB |

| 英文描述: | Up to 5A ULDO linear regulator |

| 中文描述: | CPU系统时钟发生器| SSOP封装| 56PIN |塑料 |

| 文件页数: | 6/18页 |

| 文件大小: | 268K |

| 代理商: | C9812DYB |

Low EMI Clock Generator for Intel

810E Chipset Systems

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07053 Rev. **

05/03/01

Page 6 of 18

APPROVED PRODUCT

C9812

2-Wire SMBUS Control Interface

The 2-wire control interface implements a write slave only interface according to SMBus specification. (See Fig. 7 / P. 8).

The device can be read back by using standard SMBUS command bytes. Sub addressing is not supported, thus all

preceding bytes must be sent in order to change one of the control bytes. The 2-wire control interface allows each clock

output to be individually enabled or disabled. 100 Kbits/second (standard mode) data transfer is supported.

During normal data transfer, the SDATA signal only changes when the SDCLK signal is low, and is stable when SDCLK

is high. There are two exceptions to this. A high to low transition on SDATA while SDCLK is high is used to indicate the

start of a data transfer cycle. A low to high transition on SDATA while SDCLK is high indicates the end of a data transfer

cycle. Data is always sent as complete 8-bit bytes, after which an acknowledge is generated. The first byte of a transfer

cycle is an 8-bit address. W#=0 in write mode.

The device will respond to writes to 10 bytes (max) of data to address

D2

by generating the acknowledge (low) signal on

the SDATA wire following reception of each byte. Data is transferred MSB first at a max rate of 100kbits/S. The device

will not respond to any other control interface conditions, and previously set control registers are retained.

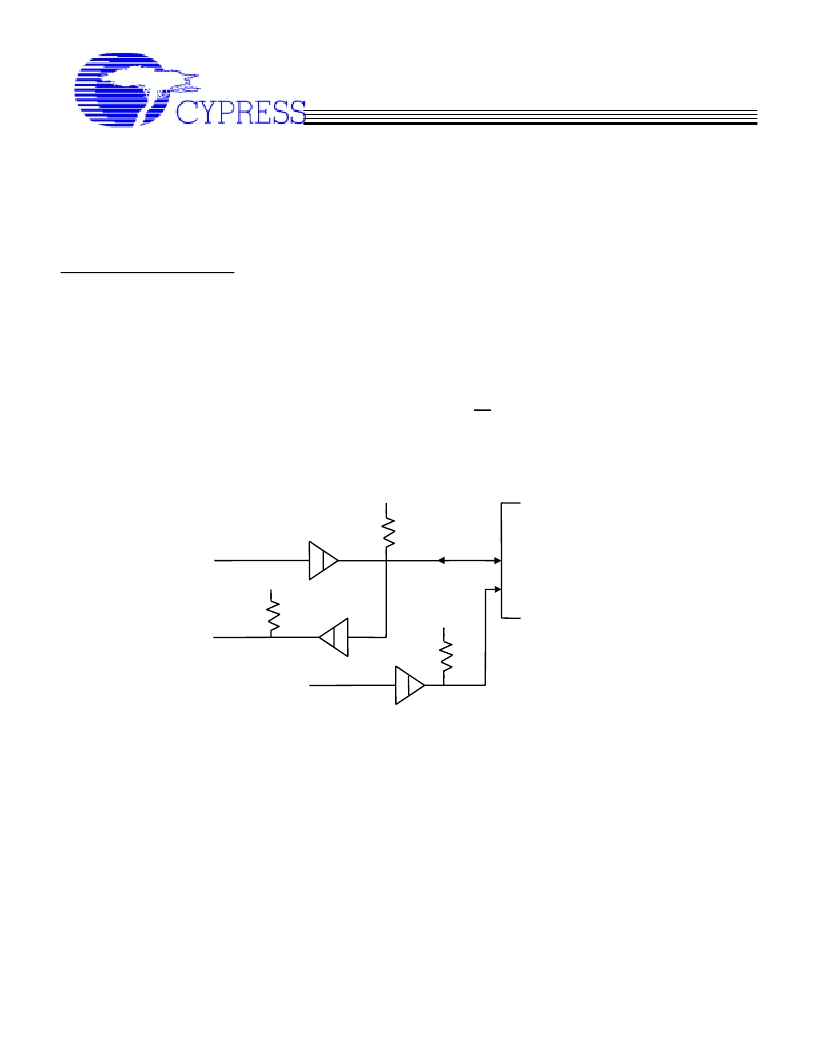

SMBUS Test Circuitry

Fig.6

Note: Buffer is 7407 with VCC @ 5.0 V

2.2 K

Device under Test

SDATA

DATAIN

SCLK

DATAOUT

CLOCK

+ 5V

+ 5V

+ 5V

2.2 K

2.2 K

相关PDF资料 |

PDF描述 |

|---|---|

| C9815DY | Up to 5A ULDO linear regulator |

| C9821GQ | Up to 5A ULDO linear regulator |

| C9822EQ | Up to 5A ULDO linear regulator |

| C9827JT | Up to 5A ULDO linear regulator |

| C9827JY | Up to 5A ULDO linear regulator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| C98130-A1231-C30 | 制造商:Siemens 功能描述: |

| C9815DY | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC |

| C981FFN-CTN | 制造商:Thomas & Betts 功能描述:1" FSC 1-GANG WP BOX 18 CU IN-CAN |

| C981U103MYVDAA7317 | 功能描述:瓷片电容器 250volts 0.01uF 20% Y5V RoHS:否 制造商:Kemet 电容:0.01 uF 容差:20 % 电压额定值:250 V 工作温度范围: 损耗因数 DF: 端接类型:Radial 产品:AC Line Rated Class X1/Y2 Capacitors |

| C981U103MYVDAAWL20 | 功能描述:10000pF 400VAC 陶瓷电容器 Y5V(F) 径向,圆盘 0.591" 直径(15.00mm) 制造商:kemet 系列:C900 包装:散装 零件状态:有效 电容:10000pF 容差:±20% 电压 - 额定:400VAC 温度系数:Y5V(F) 安装类型:通孔 工作温度:-40°C ~ 125°C 应用:安全 等级:X1,Y2 封装/外壳:径向,圆盘 大小/尺寸:0.591" 直径(15.00mm) 高度 - 安装(最大值):- 厚度(最大值):- 引线间距:0.394"(10.00mm) 特性:- 引线形式:直形 标准包装:500 |

发布紧急采购,3分钟左右您将得到回复。