- 您现在的位置:买卖IC网 > PDF目录16834 > CDB5464U (Cirrus Logic Inc)BOARD EVAL FOR CS5464 ADC PDF资料下载

参数资料

| 型号: | CDB5464U |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 14/46页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS5464 ADC |

| 标准包装: | 1 |

| 主要目的: | 电源管理,电度表/功率表 |

| 嵌入式: | 是,MCU,8 位 |

| 已用 IC / 零件: | CS5464 |

| 主要属性: | 电能表 |

| 次要属性: | 图形用户接口,SPI? 和 USB 接口 |

| 已供物品: | 板,线缆,软件 |

| 产品目录页面: | 754 (CN2011-ZH PDF) |

| 相关产品: | CS5464-ISZR-ND - IC ENERGY METERING 1PHASE 28SSOP 598-1194-5-ND - IC ENERGY METERING 1PHASE 28SSOP 598-1193-5-ND - IC PWR/ENERGY METER 3CH 28-SSOP |

| 其它名称: | 598-1554 CDB-5464U |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

�� �

�

�

�CS5464�

�V1� OFF� V1� GAIN�

�FGA�

�I1� OFF�

�I1� GAIN�

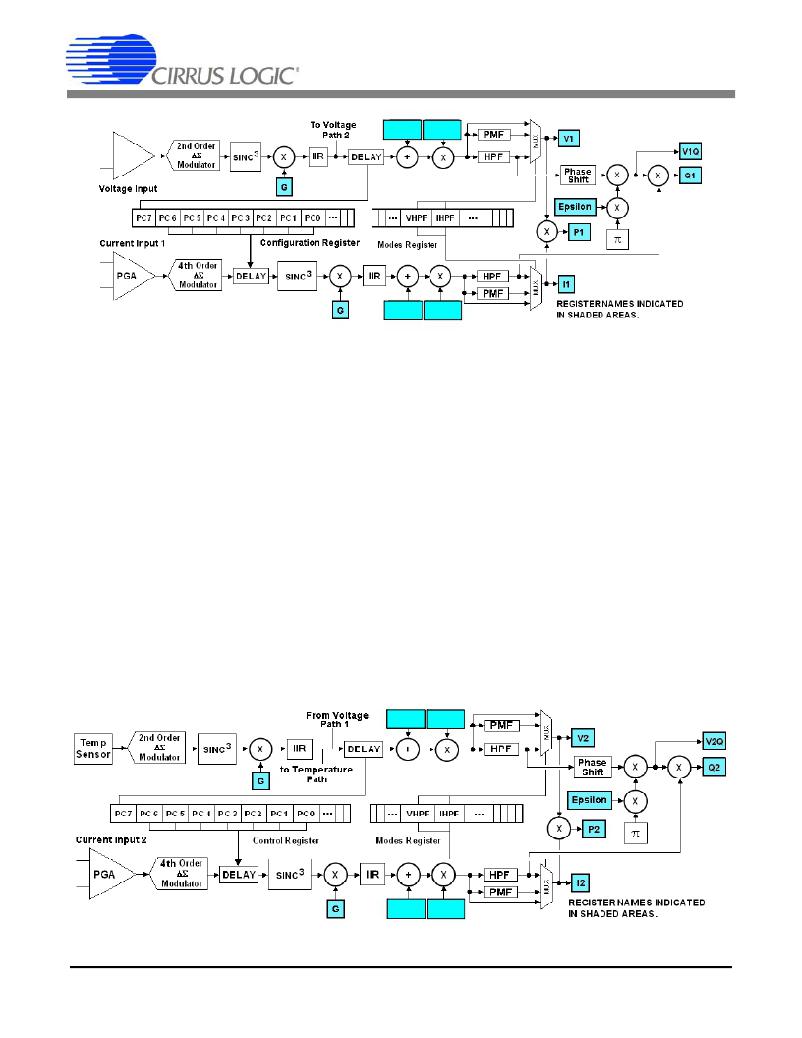

�Figure� 3.� Signal� Flow� for� V1,� I1,� P1,� Q1� Measurements�

�4.� SIGNAL� PATH� DESCRIPTION�

�The� data� flow� for� voltage� and� current� measurement� and�

�the� other� calculations� are� shown� in� Figures� 3� ,� 4� ,� and� 5� .�

�The� data� flow� consists� of� two� current� paths� and� two� volt-�

�age� paths.� Both� voltage� paths� are� derived� from� the�

�same� differential� input� pins.� Each� current� path� has� its�

�own� differential� input� pins.�

�4.1� Analog-to-Digital� Converters�

�The� voltage� and� temperature� channels� use� second-or-�

�der� delta-sigma� modulators� and� the� two� current� chan-�

�nels� use� fourth-order� delta-sigma� modulators� to� convert�

�the� analog� inputs� to� single-bit� digital� data� streams.� The�

�converters� sample� at� a� rate� of� DCLK/8.� This� high� sam-�

�pling� provides� a� wide� dynamic� range� and� simplifies� an-�

�ti-alias� filter� design.�

�4.2� Decimation� Filters�

�The� single-bit� modulator� output� data� is� widened� to�

�24� bits� and� down-sampled� to� DCLK/1024� with� low-pass�

�decimation� filters.� These� decimation� filters� are� third-or-�

�der� Sinc.� Their� outputs� are� passed� through� third-order�

�IIR� “anti-sinc”� filters,� used� to� compensate� for� the� ampli-�

�tude� roll-off� of� the� decimation� filters.�

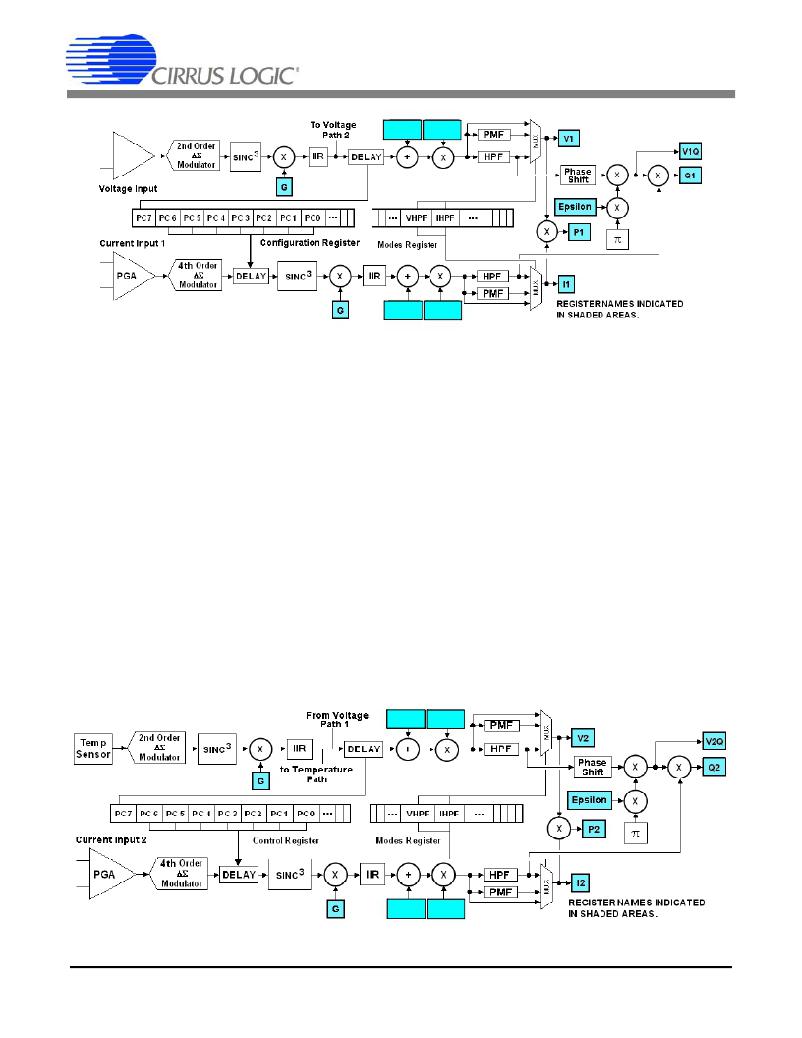

�4.3� Phase� Compensation�

�Phase� compensation� changes� the� phase� of� current� rel-�

�ative� to� voltage� by� changing� the� sampling� time� in� the�

�decimation� filters.� The� amount� of� phase� shift� is� set� by�

�bits� PC[7:0]� in� the� Configuration� register� (� Config� )� for�

�channel� 1� and� bits� PC[7:0]� in� the� Control� register� (� Ctrl� )�

�for� channel� 2.�

�Phase� compensation,� PC[7:0]� is� a� signed� two’s� comple-�

�ment� binary� value� in� the� range� of� -1.0� to� almost� +1.0�

�output� word� rate� (OWR)� samples.� For� a� sample� rate� of�

�4000� Hz,� the� delay� range� is� ±250� ?� S,� a� phase� shift� of�

�±4.5°� at� 50� Hz� and� ±5.4°� at� 60� Hz.� The� step� size� would�

�be� 0.0352°� at� 50� Hz� and� 0.0422°� at� 60� Hz� at� this� sample�

�rate.�

�V2� OFF� V2� GAIN�

�I2� OFF�

�I2� GAIN�

�Figure� 4.� Signal� Flow� for� V2,� I2,� P2,� Q2� Measurements�

�14�

�DS682F3�

�相关PDF资料 |

PDF描述 |

|---|---|

| H6MMS-2618M | DIP CABLE - HDM26S/AE26M/HDM26S |

| MAX6126A41+T | IC VREF SERIES PREC 4.096V 8UMAX |

| H1DXH-3436G | IDC CABLE - HKR34H/AE34G/X |

| PCMB104T-2R0MS | COIL 2.0 UH POWER CHOKE 20% SMD |

| MAX6126A30+T | IC VREF SERIES PREC 3V 8-UMAX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB5464U-Z | 制造商:Cirrus Logic 功能描述:EVAL BD PB-FREE DEMO BOARD FOR CS5464 - Boxed Product (Development Kits) 制造商:Cirrus Logic 功能描述:Eval Board |

| CDB5466U | 功能描述:数据转换 IC 开发工具 Eval Bd F/Residental Pow-Meter Apps RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| CDB5466U-Z | 制造商:Cirrus Logic 功能描述:PB-FREEEVAL BOARD FOR CS5466 WITH USB - Bulk |

| CDB5467U | 功能描述:数据转换 IC 开发工具 Eval Bd 4-Ch Sngl-Phs Pow/Energy RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| CDB5471 | 制造商:Cirrus Logic 功能描述:Tools Development kit Kit Con |

发布紧急采购,3分钟左右您将得到回复。