- 您现在的位置:买卖IC网 > Datasheet目录214 > CM1231-02SO (ON Semiconductor)DIODE ESD CLAMP 2CH SOT23-6 Datasheet资料下载

参数资料

| 型号: | CM1231-02SO |

| 厂商: | ON Semiconductor |

| 文件页数: | 4/12页 |

| 文件大小: | 0K |

| 描述: | DIODE ESD CLAMP 2CH SOT23-6 |

| 标准包装: | 3,000 |

| 电极标记: | 2 通道阵列 - 双向 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | SOT-23-6 |

| 供应商设备封装: | SOT-23-6 |

| 包装: | 带卷 (TR) |

| 其它名称: | CM1231-02SO-ND CM1231-02SOOSTR |

�� �

�

CM1231� ?� 02SO�

�SINGLE� AND� DUAL� CLAMP� ESD� PROTECTION�

�The� following� sections� describe� the� standard� single� clamp� ESD� protection� device� and� the� dual� clamp� ESD� protection�

�architecture� of� the� CM1231� ?� 02SO.�

�Single� Clamp� ESD� Protection�

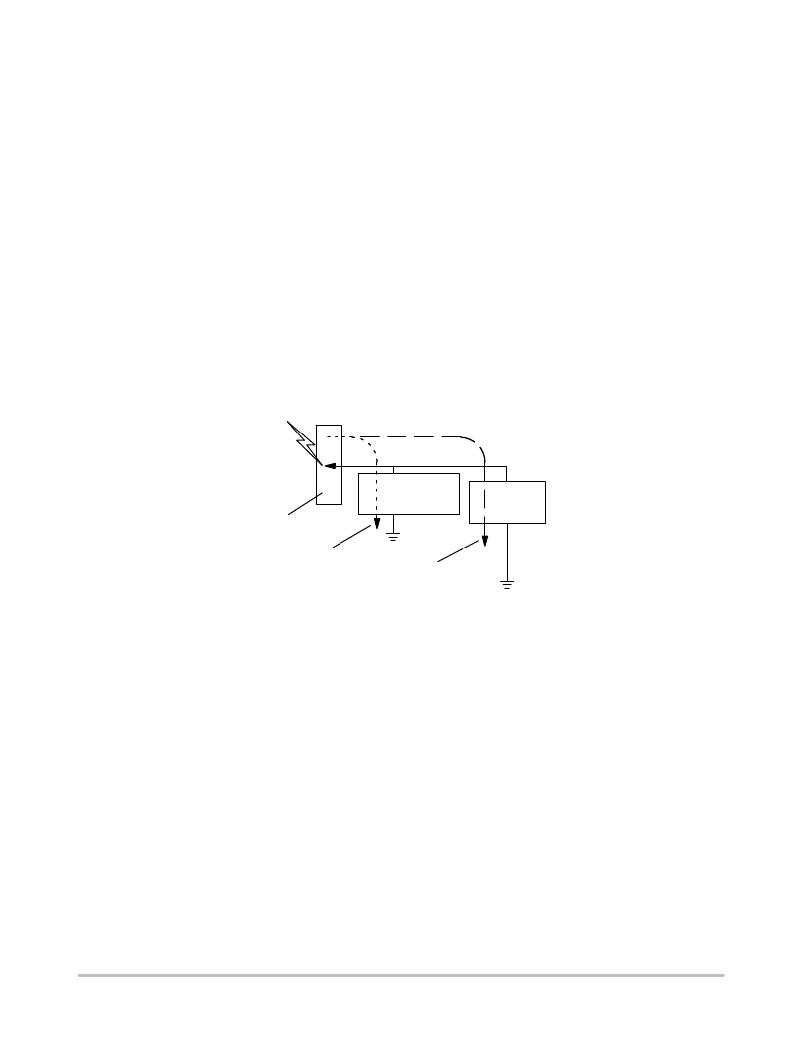

�Conceptually,� an� ESD� protection� device� performs� the� following� actions� upon� a� strike� of� ESD� discharge� into� the� protected�

�ASIC� (see� Figure� 1).�

�1.� When� an� ESD� potential� is� applied� to� the� system�

�under� test� (contact� or� air� ?� discharge),� Kirchoff� ’s�

�Current� Law� (KCL)� dictates� that� the� Electrical�

�Overstress� (EOS)� currents� will� immediately� divide�

�throughout� the� circuit,� based� on� the� dynamic�

�impedance� of� each� path�

�2.� Ideally,� the� classic� shunt� ESD� clamp� will� switch�

�within� 1� ns� to� a� low� ?� impedance� path� and� return� the�

�majority� of� the� EOS� current� to� the� chassis�

�shield/reference� ground.� In� actuality,� if� the� ESD�

�component’s� response� time� (t� CLAMP� )� is� slower� than�

�the� ASIC� it� is� protecting,� or� if� the� Dynamic�

�ESD� Strike�

�ESD�

�Resistance� (R� DYN� )� is� not� significantly� lower� than�

�the� ASIC’s� I/O� cell� circuitry,� then� the� ASIC� will� have�

�to� absorb� a� large� amount� of� the� EOS� energy,� and� may�

�be� more� likely� to� fail.�

�3.� Subsequent� to� the� ESD/EOS� event,� both� devices�

�must� immediately� return� to� their� original�

�specifications,� ready� for� an� additional� strike.� Any�

�deterioration� in� parasitics� or� clamping� capability�

�should� be� considered� a� failure,� as� it� can� affect� signal�

�integrity� or� subsequent� protection� capability� (this� is�

�known� as� “multi� ?� strike”� capability.)�

�Protection�

�Device�

�ASIC�

�I/O� Connector�

�I� SHUNT�

�I� RESIDUAL�

�Figure� 1.� Single� Clamp� ESD� Protection� Block� Diagram�

�Dual� Clamp� ESD� Protection�

�In� the� CM1231� ?� 02SO� dual� clamp� PicoGuard� XP� t�

�architecture,� the� first� stage� begins� clamping� immediately,� as�

�it� does� in� the� single� clamp� case.� The� dramatically� reduced�

�I� RES� current� from� stage� one� passes� through� the� 1� W� series�

�element� and� then� gradually� feeds� into� the� stage� two� ESD�

�device� (see� Figure� 2).� The� series� inductive� and� resistive�

�elements� further� limit� the� current� into� the� second� stage,� and�

�This� disconnection� between� the� outside� node� and� the�

�inside� ASIC� node� allows� the� stage� one� clamps� to� turn� on� and�

�remain� in� the� shunt� mode� before� the� ASIC� begins� to� shunt�

�the� reduced� residual� pulse.� This� gives� the� advantage� to� the�

�ESD� component� in� the� current� division� equation,� and�

�dramatically� reduces� the� residual� energy� that� the� ASIC� must�

�dissipate.�

�greatly� attenuate� the� resultant� peak� incident� pulse� presented�

�at� the� ASIC� side� of� the� device.�

�http://onsemi.com�

�4�

�相关PDF资料 |

PDF描述 |

|---|---|

| CM1233-08DE | DIODE ESD CLAMP ARRAY 8CH 16WDFN |

| CM1234-08DE | IC ESD PROTECT ARRAY HS 16TDFN |

| CM1235-08DE | DIODE ESD CLAMP ARRAY 8CH 16WDFN |

| CM1236-08DE | ARRAY ESD PROT HI SPD 8CH 16TDFN |

| CM1241-04D4 | IC ESD PROT ARRAY ESD LOCAP 8DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CM1232 | 制造商:CALMIRCO 制造商全称:California Micro Devices Corp 功能描述:CMOS MICROPROCESSOR MONITOR CIRCUIT |

| CM1232F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| CM1232IF | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| CM1232IP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| CM1232IS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

发布紧急采购,3分钟左右您将得到回复。