参数资料

| 型号: | CP80C86-2Z |

| 厂商: | Intersil |

| 文件页数: | 34/37页 |

| 文件大小: | 0K |

| 描述: | IC CPU 16BIT 5V 8MHZ 40-PDIP |

| 标准包装: | 9 |

| 处理器类型: | 80C86 16-位 |

| 速度: | 8MHz |

| 电压: | 4.5 ~ 5.5V |

| 安装类型: | 通孔 |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 供应商设备封装: | 40-DIP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页

6

FN2957.3

January 9, 2009

HOLD

HLDA

31, 30

I

O

HOLD: indicates that another master is requesting a local bus “hold”. To be an acknowledged, HOLD

must be active HIGH. The processor receiving the “hold” will issue a “hold acknowledge” (HLDA) in

the middle of a t4 or TI clock cycle. Simultaneously with the issuance of HLDA, the processor will float

the local bus and control lines. After HOLD is detected as being LOW, the processor will lower HLDA,

and when the processor needs to run another cycle, it will again drive the local bus and control lines.

HOLD is not an asynchronous input. External synchronization should be provided if the system cannot

otherwise guarantee the setup time.

Minimum Mode System (Continued)

The following pin function descriptions are for the 80C86 in minimum mode (i.e., MN/MX = VCC). Only the pin functions which are unique to minimum

mode are described; all other pin functions are as described in the following.

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

Maximum Mode System

The following pin function descriptions are for the 80C86 system in maximum mode (i.e., MN/MX - GND). Only the pin functions which are unique

to maximum mode are described in the following.

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

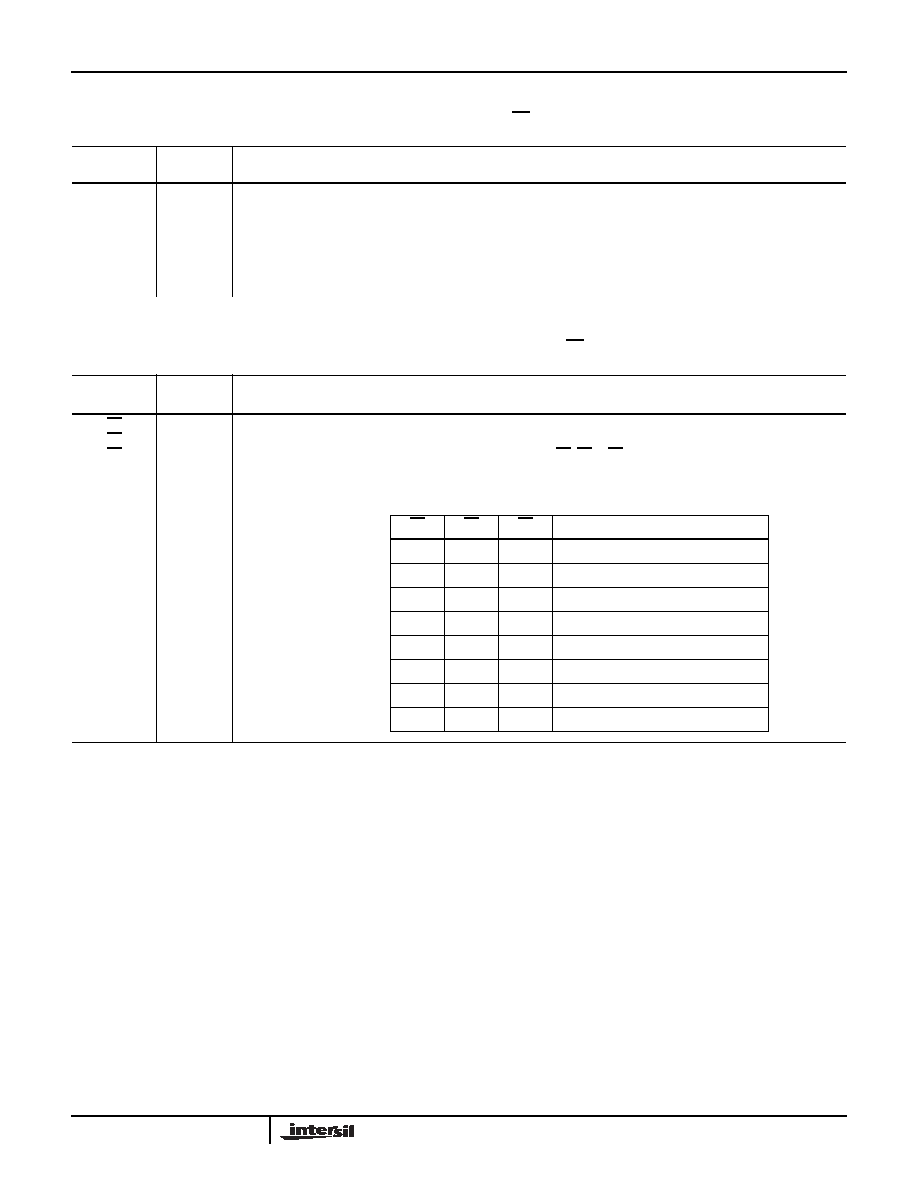

S0

S1

S2

26

27

28

O

STATUS: is active during t4, t1 and t2 and is returned to the passive state (1, 1, 1) during t3 or during

tW when READY is HIGH. This status is used by the 82C88 Bus Controller to generate all memory

and I/O access control signals. Any change by S2, S1 or S0 during t4 is used to indicate the beginning

of a bus cycle, and the return to the passive state in t3 or tW is used to indicate the end of a bus cycle.

These signals are held at a high impedance logic one state during “grant sequence”.

S2

S1

S0

CHARACTERISTICS

0

Interrupt Acknowledge

0

1

Read I/O Port

0

1

0

Write I/O Port

011

Halt

1

0

Code Access

1

0

1

Read Memory

1

0

Write Memory

1

Passive

80C86

相关PDF资料 |

PDF描述 |

|---|---|

| CP82C50A-5Z | IC ASYNC COMM ELEMENT UART 40DIP |

| CP82C89 | IC ARBITER BUS 5V 8MHZ 20-DIP |

| CPC1465D | IC DC TERMINATION 16-SOIC |

| CPC1465M | IC SHDSL/ISDN DC TERM 16MLP |

| CPC2400E | MODULE MODEM 2400BAUD EMBEDDEDED |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CP80C86R2489 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| CP80C88 | 功能描述:微处理器 - MPU CPU 8/16BIT 5V 5MHZ 40PDIP COM RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| CP80C88-2 | 功能描述:微处理器 - MPU CPU 8/16BIT 5V 8MHZ 40PDIP COM RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| CP80C88-2Z | 功能描述:IC PWM CONTROLLER RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:40 系列:MPC83xx 处理器类型:32-位 MPC83xx PowerQUICC II Pro 特点:- 速度:267MHz 电压:0.95 V ~ 1.05 V 安装类型:表面贴装 封装/外壳:516-BBGA 裸露焊盘 供应商设备封装:516-PBGAPGE(27x27) 包装:托盘 |

| CP80C88R2489 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。