- 您现在的位置:买卖IC网 > PDF目录380066 > CS4215-KQ (CIRRUS LOGIC INC) 16-Bit Multimedia Audio Codec PDF资料下载

参数资料

| 型号: | CS4215-KQ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 16-Bit Multimedia Audio Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 11/52页 |

| 文件大小: | 878K |

| 代理商: | CS4215-KQ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

after power up. A calibration cycle will occur

immediately after leaving the reset state. A cali-

bration cycle will also occur immediately after

going from control mode to data mode (D/C go-

ing high). When powering up the CS4215, or

exiting the power down state, a minimum of

50 ms must occur, to allow the voltage reference

to settle, before initiating a calibration cycle.

This is achieved by holding RESET low or stay-

ing in control mode for 50 ms after power up or

exiting power down mode. The input offset error

will be calibrated for whichever input channel is

selected (microphone or line, using the IS bit).

Therefore, the IS bit should remain steady while

the codec is calibrating, although the other bits

input to the codec are ignored. Calibration takes

194 FSYNC cycles and SDOUT data bits will be

zero during this period. The A/D Invalid bit, ADI

(bit 7 in data time slot 6), will be high during

calibration and will go low when calibration is

finished.

Parallel Input/Output

Two pins are provided for parallel input/output.

These pins are open drain outputs and require

external pull-up resistors. Writing a zero turns on

the output transistor, pulling the pin to ground;

writing a one turns off the output transistor,

which allows an external resistor to pull the pin

high. When used as an input, a one must be writ-

ten to the pin, thereby allowing an external

device to pull it low or leave it high. These pins

can be read in control mode and their state is

recorded in Control Register 5. These pins can

be written to and read back in data mode using

Data Register 7. Figure 5 shows the Parallel In-

put/Output timing.

Notes:

4.

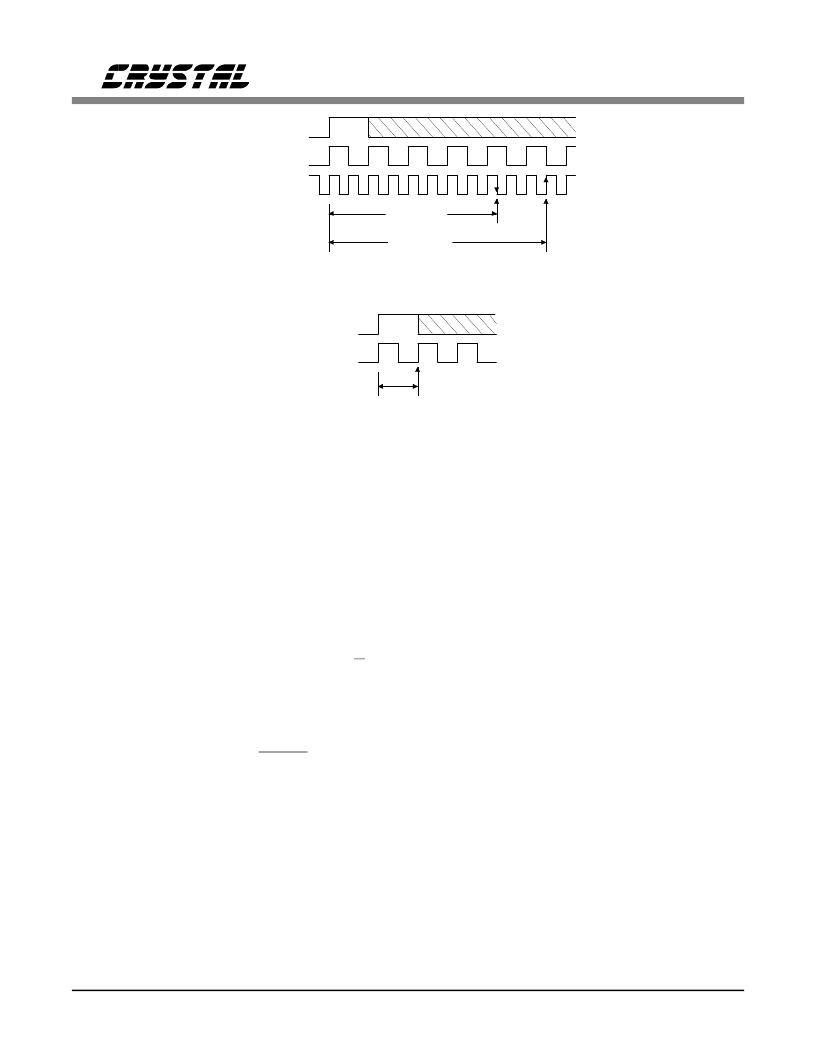

CONTROL MODE READ - The PIO pins are sampled by a rising edge of SCLK.

3.

DATA MODE READ, WRITE - are tied to the rising edge of FSYNC and CLKOUT.

They are independent of SCLK.

2.

CONTROL MODE READ - The data is sent out, via SDOUT, the same frame.

1.

DATA MODE READ - The data is sent out via SDOUT on the next frame.

Data Mode -Read and Write

Control Mode - Read Only

TSIN

SCLK

1 SCLK

PIO Read

PIO Read

PIO Write

8.5 CLKOUT's

11 CLKOUT's

SCLK

CLKOUT

FSYNC

Figure 5. PIO Pin Timing

CS4215

DS76F2

11

相关PDF资料 |

PDF描述 |

|---|---|

| CS4215 | 16-Bit Multimedia Audio Codec |

| CS4216 | 16-Bit Stereo Audio Codec |

| CS4216-KL | IC EEPROM SRL 256-8BIT 8DIP |

| CS4216-KQ | 16-Bit Stereo Audio Codec |

| CS4218-KL | 16-Bit Stereo Audio Codec |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4216 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4216-KL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS4216-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4217-KL | 制造商:CRYSTAL 功能描述: |

| CS4218 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

发布紧急采购,3分钟左右您将得到回复。