- 您现在的位置:买卖IC网 > PDF目录380066 > CS4215-KQ (CIRRUS LOGIC INC) 16-Bit Multimedia Audio Codec PDF资料下载

参数资料

| 型号: | CS4215-KQ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 16-Bit Multimedia Audio Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 12/52页 |

| 文件大小: | 878K |

| 代理商: | CS4215-KQ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Clock Generation

The master clock operating the CS4215 may be

generated using the on-chip crystal oscillators, or

by using an external clock source. In all data

modes SCLK and FSYNC must be synchronous

to the selected master clock.

If the master clock source stops, the digital fil-

ters will power down after 5

μ

s to prevent

overheating. If FSYNC stops, the digital filters

will power down after approximately 1 FSYNC

period. The CS4215 will not enter the total

power down state.

Internal Clock Generation

Two external crystals may be attached to the

XTL1IN, XTL1OUT, XTL2IN and XTL2OUT

pins. Use of an external crystal requires addi-

tional 40 pF loading capacitors to digital ground

(see Figure 1). XTAL1 oscillator is intended for

use at 24.576 MHz and XTAL2 oscillator is in-

tended for use at 16.9344 MHz, although other

frequencies may be used. The gain of the inter-

nal inverter is slightly higher for XTAL1,

ensuring proper operation at >24 MHz frequen-

cies. The crystals should be parallel resonant,

fundamental mode and designed for 20 pF load-

ing (equivalent to a 40 pF capacitor on each leg).

If XTAL1 or XTAL2 is not selected as the mas-

ter clock, that particular crystal oscillator is

powered down to minimize interference. If a

crystal is not needed, the XTL-IN pin should be

grounded. An example crystal supplier is CAL

Crystal, telephone number (714) 991-1580.

FSYNC and SCLK must be synchronous to the

master clock. When using the codec in slave

mode with one of the crystals as master clock,

the controller must derive FSYNC and SCLK

from the crystals, i.e. via CLKOUT. Note that

CLKOUT will stop in a low condition within

two periods after D/C goes low.

An internally generated clock which is 256 times

the sample rate (FSYNC rate) is output

(CLKOUT) for potential use with an external

AES/EBU transmitter, or another CS4215. No

glitch occurs on CLKOUT when selecting alter-

nate clock sources. CLKOUT will stop in a low

condition within two periods after D/C goes low,

assuming one of the crystal oscillators is se-

lected, or either CLKIN or SCLK is the master

clock source and is continuous. The duty cycle

of CLKOUT is 50% if the master clock is one of

the crystal oscillators and the DFR bits are 0, 1,

2, 6 or 7. If the DFR bits are 3 or 5, the duty

cycle is 33% (high time). If the DFR bits are 4

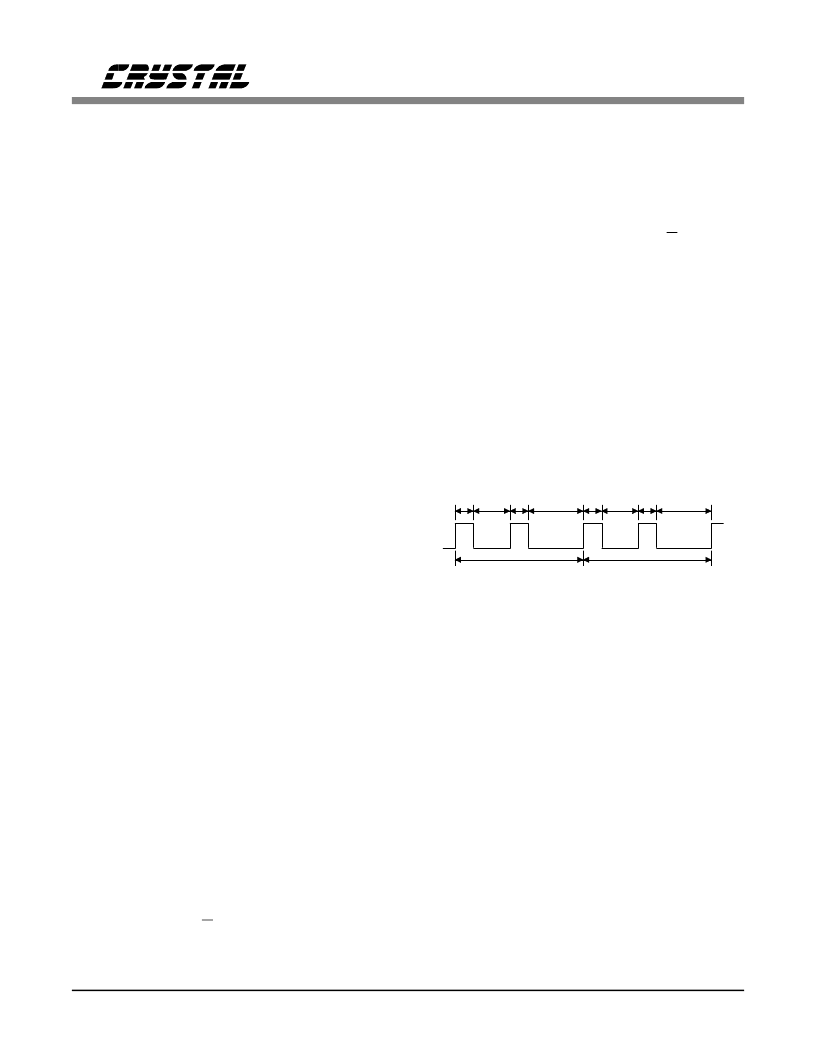

then CLKOUT has the timing shown in Figure 6.

If the master clock is SCLK or CLKIN, the duty

cycle of CLKOUT will be the same as the mas-

ter clock source.

External Clock

An external clock input pin (CLKIN) is provided

for potential use with an external AES/EBU re-

ceiver, or an already existing system clock.

When MCK2 = 0, the input clock must be ex-

actly 256 times the sample rate, and FSYNC and

SCLK must be synchronous to CLKIN. When

MCK2 = 1 the DFR bits allow various divide

ratios off the CLKIN frequency.

Alternatively, an external high frequency clock

may be driven into XTL1IN or XTL2IN. The

correct clock source must be selected using the

MCK bits. Manipulating DFR bits will allow

various divide ratios from the clock to be se-

1

2

1

3

1/(128 x FSYNC)

1/(128 x FSYNC)

1

2

1

3

Figure 6. CLKOUT duty cycle using the on-chip

crystal oscillator when DFR = 4

( typically FSYNC = 37.8 kHz)

CS4215

12

DS76F2

相关PDF资料 |

PDF描述 |

|---|---|

| CS4215 | 16-Bit Multimedia Audio Codec |

| CS4216 | 16-Bit Stereo Audio Codec |

| CS4216-KL | IC EEPROM SRL 256-8BIT 8DIP |

| CS4216-KQ | 16-Bit Stereo Audio Codec |

| CS4218-KL | 16-Bit Stereo Audio Codec |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4216 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4216-KL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS4216-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4217-KL | 制造商:CRYSTAL 功能描述: |

| CS4218 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

发布紧急采购,3分钟左右您将得到回复。