参数资料

| 型号: | CS5373A-ISZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 19/40页 |

| 文件大小: | 0K |

| 描述: | IC DAC/MODULATOR LP/HP 28-SSOP |

| 标准包装: | 1,000 |

| 类型: | 调制器 |

| 分辨率(位): | 24 b |

| 采样率(每秒): | 512k |

| 电压电源: | 模拟和数字,双 ± |

| 电源电压: | ± 2.5V,3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 28-SSOP |

| 包装: | 带卷 (TR) |

| 配用: | CDB5378-ND - EVALUATION BOARD FOR CS5378 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

CS5373A

26

DS703F2

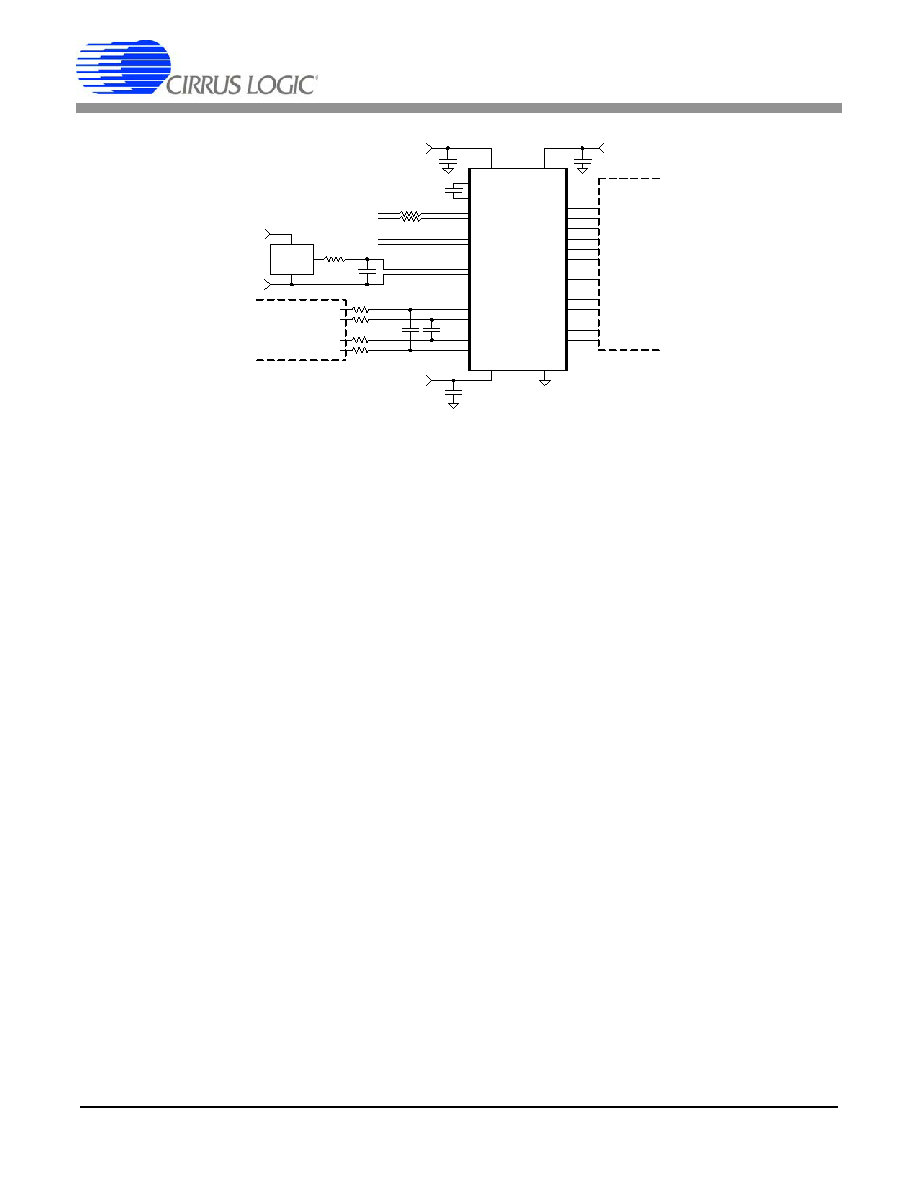

6. DIGITAL SIGNALS

The CS5373A is designed to operate with the

CS5378 digital filter. The digital filter gener-

ates the master clock and synchronization sig-

nals (MCLK and MSYNC) while receiving back

the modulator one-bit

ΔΣ conversion data

(MDATA) and over-range flag (MFLAG). It

also generates digital one-bit

ΔΣ test bit

stream data for the test DAC (TDATA) and

controls GPIO pins to set the operational

mode (MODE) and attenuation (ATT).

6.1 MCLK Connection

The CS5378 digital filter generates the master

clock for CS5373A, typically 2.048 MHz, from

a synchronous CLK input from the external

system. By default, MCLK is disabled at reset

and is enabled by writing the digital filter CON-

FIG register. If MCLK is disabled during oper-

ation, the CS5373A will enter power down

after approximately 40

S.

MCLK must have low in-band jitter to guaran-

tee full analog performance, requiring a crys-

tal- or VCXO-based system clock into the

digital filter. Clock jitter on the digital filter ex-

ternal CLK input directly translates to jitter on

MCLK.

6.2 MSYNC Connection

The CS5378 digital filter also provides a syn-

chronization signal to the CS5373A. The

MSYNC signal is generated following a rising

edge received on the digital filter SYNC input.

By default MSYNC generation is disabled at

reset and is enabled by writing to the digital fil-

ter CONFIG register.

The input SYNC signal to the CS5378 digital

filter sets a common reference time t0 for mea-

surement events, thereby synchronizing ana-

log sampling across a measurement network.

The timing accuracy of the received SYNC sig-

nal from node to node must be +/- 1 MCLK to

maximize the MSYNC analog sample syn-

chronization accuracy.

The CS5373A MSYNC input is rising-edge

triggered and resets the internal MCLK coun-

ter/divider to guarantee synchronous opera-

tion with other system devices. While the

MSYNC signal synchronizes the internal oper-

ation of the CS5373A, by default, it does not

synchronize the phase of the incoming encod-

ed digital test bit stream (TBS) sine wave un-

less enabled in the digital filter TBSCFG

register.

CS5373A

TDATA

CAP +

CAP -

BUF+

BUF-

OUT+

OUT-

MCLK

M SYNC

GND

MODE1

MODE2

ATT 0

ATT 1

MODE0

ATT 2

VA -

2.5 V

VREF

10

Ω

VREF +

VREF -

100 F

0.1 F

VA+

VA +

VD

0. 1F

0.1F

VD

VA+

10 nF

C0 G

GPIO

CS5378

SIGNALS

MCLK

M SYNC

TBSDATA

GPIO

SENSOR

TEST OUTPUT

ELECTRONICS

TEST OUTPUT

VA-

+

VA-

Route VREF as diff pair

Route OUT as diff pair

Route BUF as diff pair

MDATA

MFLAG

MDATA

MFLAG

INR+

INF+

INF-

INR-

20 nF

*

C0G

20 nF

*

C0 G

INPUT FROM

CS 3301 A/02 A

AM PLIFIER

*Populate with 2 x 10 nF or

1 x 22 nF C0 G or better .

680

Ω

680

Ω

680

Ω

680

Ω

Figure 13. Digital Signals

相关PDF资料 |

PDF描述 |

|---|---|

| CS5376A-IQZ | IC FILTER DGTL MULTI-CH 64-TQFP |

| CS61577-IL1Z | IC LINE INTERFACE T1/E1 28PLCC |

| CS61584A-IQ3Z | IC LINE INTERFACE T1/E1 64LQFP |

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5374 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Dual High-performance Amplifier & ΔΣ Modulator |

| CS5374_0910 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Dual High-performance Amplifier & ΔΣ Modulator |

| CS5374-CNZ | 功能描述:差分放大器 2-Ch DS Modulator & Hydrophone RoHS:否 制造商:Texas Instruments 通道数量:1 Channel 带宽:2.4 GHz 可用增益调整:6 dB to 26 dB 输入补偿电压: 共模抑制比(最小值):- 40 dB 工作电源电压:4.75 V to 5.25 V 电源电流:100 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:WQFN-24 封装:Reel |

| CS5376 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CS5376 Rev. A Errata|Geophysical|A/D Converters |

| CS5376A | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, Multi-channel Decimation Filter |

发布紧急采购,3分钟左右您将得到回复。