- 您现在的位置:买卖IC网 > PDF目录20640 > CS5463-ISZ (Cirrus Logic Inc)IC ENERGY METERING 1PHASE 24SSOP PDF资料下载

参数资料

| 型号: | CS5463-ISZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 37/46页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METERING 1PHASE 24SSOP |

| 特色产品: | CS546X IC Family |

| 标准包装: | 59 |

| 输入阻抗: | 30 千欧 |

| 测量误差: | 0.1% |

| 电压 - 高输入/输出: | 0.8V |

| 电压 - 低输入/输出: | 0.2V |

| 电流 - 电源: | 2.9mA |

| 电源电压: | 4.75 V ~ 5.25 V |

| 测量仪表类型: | 单相 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 管件 |

| 产品目录页面: | 754 (CN2011-ZH PDF) |

| 配用: | 598-1553-ND - BOARD EVAL & SOFTWARE CS5463 ADC |

| 其它名称: | 598-1096-5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

�� �

�

�

�CS5463�

�7.� SYSTEM� CALIBRATION�

�7.1� Channel� Offset� and� Gain� Calibration�

�The� CS5463� provides� digital� DC� offset� and� gain� com-�

�pensation� that� can� be� applied� to� the� instantaneous� volt-�

�age� and� current� measurements,� and� AC� offset�

�compensation� to� the� voltage� and� current� RMS� calcula-�

�tions.�

�Since� the� voltage� and� current� channels� have� indepen-�

�dent� offset� and� gain� registers,� system� offset� and/or�

�gain� can� be� performed� on� either� channel� without� the�

�calibration� results� from� one� channel� affecting� the� oth-�

�er.�

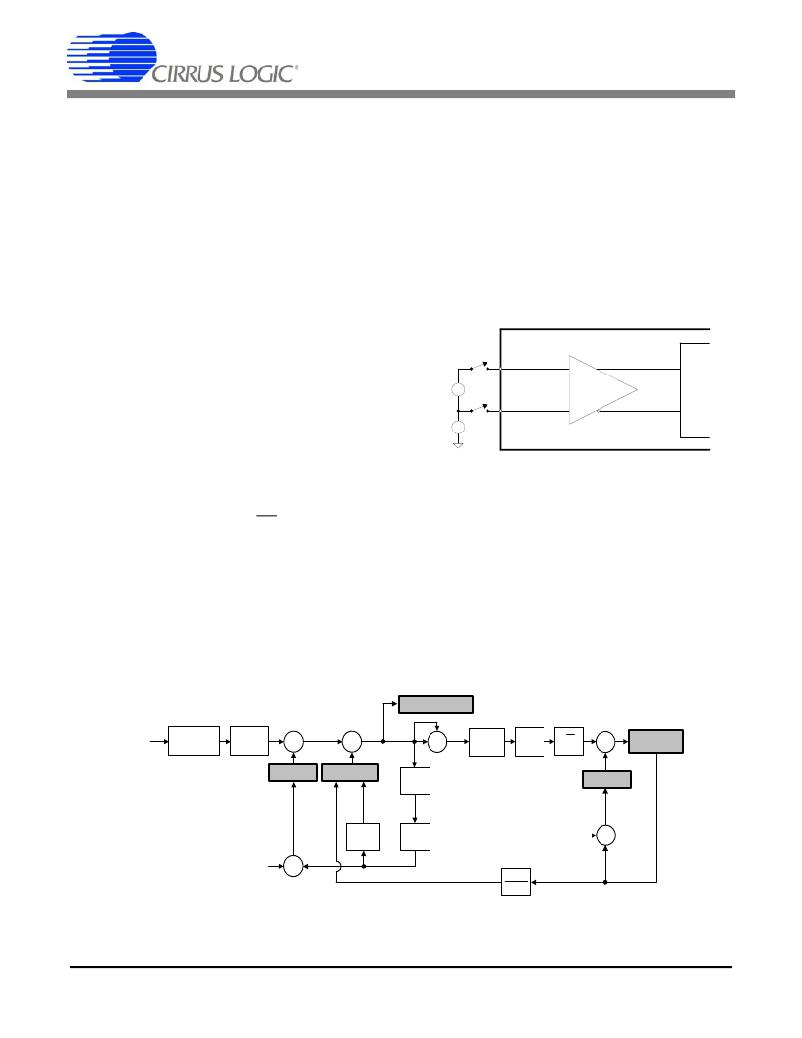

�The� computational� flow� of� the� calibration� sequences� are�

�illustrated� in� Figure� 12.� The� flow� applies� to� both� the� volt-�

�N� +� 30� conversion� cycles� to� complete.� For� AC� offset� cal-�

�ibrations,� the� sequence� takes� at� least� 6N� +� 30� ADC� cy-�

�cles� to� complete,� (about� 6� computation� cycles).� As� N� is�

�increased,� the� accuracy� of� calibration� results� will� in-�

�crease.�

�7.1.2� Offset� Calibration� Sequence�

�For� DC� and� AC� offset� calibrations,� the� VIN� ?� pins� of� the�

�voltage� and� IIN� ?� pins� of� the� current� channels� should� be�

�connected� to� their� ground� reference� level.� (see� Figure�

�13.)�

�External�

�Connections�

�age� channel� and� current� channel.�

�7.1.1� Calibration� Sequence�

�0V� +-�

�AIN+�

�+�

�XGAIN�

�+�

�The� CS5463� must� be� operating� in� its� active� state� and�

�ready� to� accept� valid� commands.� Refer� to� Section� 5.16�

�CM� +-�

�AIN-�

�-�

�-�

�Commands� on� page� 23.� The� calibration� algorithms� are�

�dependent� on� the� value� N� in� the� Cycle� Count� Register�

�(see� Figure� 12).� Upon� completion,� the� results� of� the� cal-�

�ibration� are� available� in� their� corresponding� register.�

�The� DRDY� bit� in� the� Status� Register� will� be� set.� If� the�

�DRDY� bit� is� to� be� output� on� the� INT� pin,� then� DRDY� bit�

�in� the� Mask� Register� must� be� set.� The� initial� values� in�

�the� AC� gain� and� offset� registers� do� affect� the� results� of�

�the� calibration� results.�

�7.1.1.1� Duration� of� Calibration� Sequence�

�The� value� of� the� Cycle� Count� Register� (N)� determines�

�the� number� of� conversions� performed� by� the� CS5463�

�during� a� given� calibration� sequence.� For� DC� offset� and�

�gain� calibrations,� the� calibration� sequence� takes� at� least�

�Figure� 13.� System� Calibration� of� Offset�

�The� AC� offset� registers� must� be� set� to� the� default�

�(0x000000).�

�7.1.2.1� DC� Offset� Calibration� Sequence�

�Channel� gain� should� be� set� to� 1.0� when� performing� DC�

�offset� calibration.� Initiate� a� DC� offset� calibration.� The� DC�

�offset� registers� are� updated� with� the� negative� of� the� av-�

�erage� of� the� instantaneous� samples� collected� over� a�

�computational� cycle.� Upon� completion� of� the� DC� offset�

�calibration� the� DC� offset� is� stored� in� the� corresponding�

�DC� offset� register.� The� DC� offset� value� will� be� added� to�

�to� V*,� I*� Registers�

�?�

�In�

�Modulator�

�Filter�

�+�

�+�

�+�

�X�

�X�

�N�

�?� N�

�?�

�+�

�+�

�+�

�V� RMS� *,� I� RMS� *�

�Registers�

�?�

�DC� Offset*�

�Gain*�

�N�

�AC� Offset*�

�-1�

�X�

�Inverse�

�?� N�

�-1�

�X�

�0.6�

�RMS�

�*� Denotes� readable/writable� register�

�Figure� 12.� Calibration� Data� Flow�

�DS678F3�

�37�

�相关PDF资料 |

PDF描述 |

|---|---|

| RGM40DTAD-S189 | CONN EDGECARD 80POS R/A .156 SLD |

| TTN0.38SV100 | THERMASHIELD TUBE 3/8" SLV 100' |

| ADE7751ARSZ | IC ENERGY METERING 1PHASE 24SSOP |

| RCC07DRYI-S13 | CONN EDGECARD 14POS .100 EXTEND |

| MURHB840CTT4G | DIODE ULTRA FAST 400V 4A D2PAK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5463-ISZ/D | 制造商:Cirrus Logic 功能描述: |

| CS5463-ISZR | 功能描述:电流和电力监控器、调节器 IC Single Phase PWR/Energy RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel |

| CS5463-ISZR/E2 | 制造商:Cirrus Logic 功能描述: |

| CS5464 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464_07 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

发布紧急采购,3分钟左右您将得到回复。