- 您现在的位置:买卖IC网 > PDF目录10681 > CS5525-ASZ (Cirrus Logic Inc)IC ADC 16BIT W/4BIT LATCH 20SSOP PDF资料下载

参数资料

| 型号: | CS5525-ASZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 14/30页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT W/4BIT LATCH 20SSOP |

| 标准包装: | 66 |

| 位数: | 16 |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 12.7mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 管件 |

| 输入数目和类型: | 1 个差分,单极;1 个差分,双极 |

| 产品目录页面: | 755 (CN2011-ZH PDF) |

| 配用: | 598-1013-ND - EVAL BOARD FOR CS5525 |

| 其它名称: | 598-1107-5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

CS5525 CS5526

DS202F5

21

sion. The user would then issue 8 SCLKs (with

SDI = logic 0) to clear the SDO flag. Upon the fall-

ing edge of the 8th SCLK, the SDO pin will present

the first bit (MSB) of the conversion word. 24

SCLKs (high, then low) are required to read the

conversion word from the port. The user must not

give an explicit command to read the conversion

data register when the PF bit is set to logic 1. The

data conversion word must be read before a new

command can be entered (if the SC command is

used with PF = 1).

If the CC (Continuous Conversion) command is is-

sued (CC = 1, CB =1, all other command bits = 0)

the SDO pin will go low at the completion of a con-

version. The user would then issue 8 SCLKs (with

SDI = logic 0) to clear the SDO flag. Upon the fall-

ing edge of the 8th SCLK, the SDO pin will present

the first bit (MSB) of the conversion word. 24

SCLKs (high, then low) are required to read the

conversion word from the port. The user must not

give an explicit command to read the conversion

data register when the PF bit is set to logic 1. When

operating in the continuous conversion mode, the

user need not read every conversion. If the user

does nothing after SDO falls, SDO will rise one

XIN clock cycle before the next conversion word is

available and then fall again to signal that another

conversion word is available. If the user begins to

clear the SDO flag and read the conversion data,

this action must be finished before the conversion

cycle which is occurring in the background is com-

plete if the user wants to be able to read the new

conversion data.

To exit the continuous conversion mode, issue any

valid command to the SDI input when the SDO flag

falls. If a CC command is issued to the converter

while it is performing a conversion, the filter will

restart a convolution cycle to perform a new con-

version.

Output Word Rate Selection

The WR2-WR0 bits of the configuration register

set the output conversion word rate of the convert-

ers as shown in Table 2. The word rates indicated

in the table assume a master clock of 32.768 kHz.

Upon reset the converters are set to operate with an

output word rate of 15.0 Sps.

Clock Generator

The CS5525/26 include a gate which can be con-

nected with an external crystal to provide the master

clock for the chips. They are designed to operate us-

ing a low-cost 32.768 kHz “tuning fork” type crys-

tal. The 32.768 kHz crystal should be connected as

shown in Figure 18. Lead lengths should be mini-

mized to reduce stray capacitance.

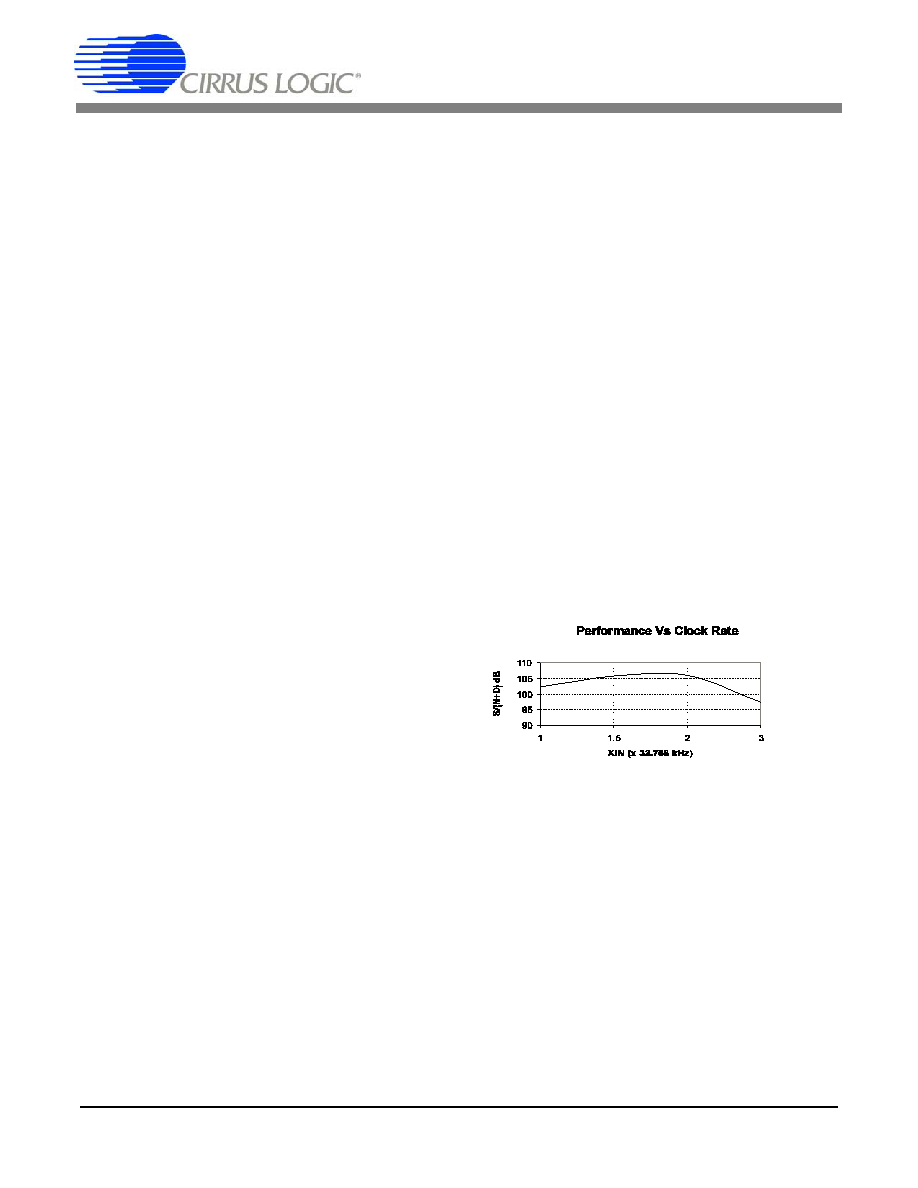

The converters will operate with an external

(CMOS compatible) clock with frequencies up to

three times the typical crystal frequency of 32.768

kHz. Figure 17 details the converter’s performance

at increased clock rates.

The 32.768 kHz crystal is normally specified as a

time-keeping crystal with tight specifications for

both initial frequency and for drift over temperature.

To maintain excellent frequency stability, these

crystals are specified only over limited operating

temperature ranges (i.e. -10 °C to +60 °C). However,

applications with the CS5525/26 don’t generally re-

quire such tight tolerances. When 32.768 kHz tuning

fork crystals are used, it is recommended that protec-

tion components, an external resistor and capacitor

as shown in Figure 18, be used.

Figure 17. High Speed Clock Performance

相关PDF资料 |

PDF描述 |

|---|---|

| LT1715IMS#TR | IC COMPARATOR 150MHZ DUAL 10MSOP |

| AD8612ARUZ-REEL | IC COMP DUAL 4NS FAST 14-TSSOP |

| AD9609BCPZ-40 | IC ADC 10BIT 40MSPS LP 32LFCSP |

| AD7276BUJZ-500RL7 | IC ADC 12BIT 3MSPS TSOT23-6 |

| LT1720IMS8#PBF | IC COMPARATOR DUAL HS 3/5V 8MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5525-ASZR | 功能描述:模数转换器 - ADC IC 16Bit Delta Sigma Multi-Range ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5525-BP | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16 BIT / 20 BIT MULTI RANGE ADC WITH 4 BIT LATCH |

| CS5525-BS | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16 BIT / 20 BIT MULTI RANGE ADC WITH 4 BIT LATCH |

| CS5526 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16 BIT / 20 BIT MULTI RANGE ADC WITH 4 BIT LATCH |

| CS5526-000 | 制造商:TE Connectivity 功能描述:S200-1-01 - Bulk |

发布紧急采购,3分钟左右您将得到回复。