- 您现在的位置:买卖IC网 > PDF目录17033 > DC1067A-B (Linear Technology)BOARD DELTA SIGMA ADC LTC2450-1 PDF资料下载

参数资料

| 型号: | DC1067A-B |

| 厂商: | Linear Technology |

| 文件页数: | 3/20页 |

| 文件大小: | 0K |

| 描述: | BOARD DELTA SIGMA ADC LTC2450-1 |

| 软件下载: | QuikEval System |

| 设计资源: | DC1067A Design File DC1067A Schematic |

| 标准包装: | 1 |

| 系列: | QuikEval™ |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 30 |

| 数据接口: | 串行,SPI? |

| 已用 IC / 零件: | LTC2450-1 |

| 已供物品: | 板 |

| 相关产品: | LTC2450IDC#TRPBF-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450IDC-1#TRPBF-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450IDC-1#TRMPBFTR-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450IDC#TRMPBFTR-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450CDC-1#TRPBF-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450CDC-1#TRMPBFTR-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450CDC#TRPBF-ND - IC ADC 16BIT DELTA SIG 6-DFN LTC2450CDC#TRMPBFTR-ND - IC ADC 16BIT DELTA SIG 6-DFN |

LTC2450

11

2450fb

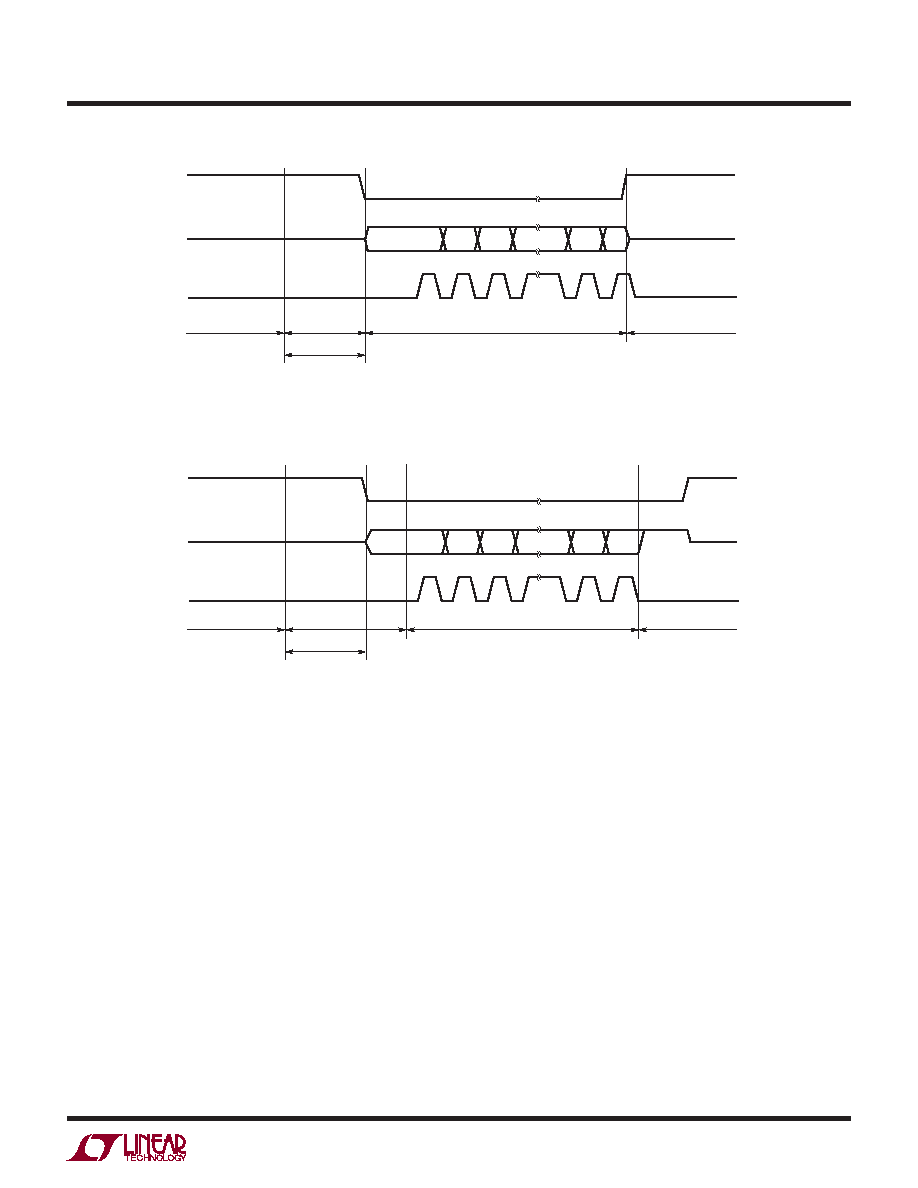

Examples of Aborting Cycle using CS

For some applications the user may wish to abort the I/O

cycle and begin a new conversion. If the LTC2450 is in the

data output state, a CS rising edge clears the remaining data

bits from memory, aborts the output cycle and triggers a

new conversion. Figure 9 shows an example of aborting

an I/O with idle-high (CPOL = 1) and Figure 10 shows an

example of aborting an I/O with idle-low (CPOL = 0).

A new conversion cycle can be triggered using the CS

signal without having to generate any serial clock pulses

as shown in Figure 11. If SCK is maintained at a LOW

logic level, after the end of a conversion cycle, a new

conversion operation can be triggered by pulling CS low

and then high. When CS is pulled low (CS = LOW), SDO

will output the most signicant bit (D15) of the result of

the just completed conversion. While a low logic level is

maintained at SCK pin and CS is subsequently pulled high

(CS = HIGH) the remaining 15 bits of the result (D14:D0)

are discarded and a new conversion cycle starts.

Following the aborted I/O, additional clock pulses in the

CONVERT state are acceptable, but excessive signal tran-

sitions on SCK can potentially create noise on the ADC

during the conversion, and thus may negatively inuence

the conversion accuracy.

APPLICATIONS INFORMATION

D15

D14

D13

D12

D2

D1

D0

SD0

clk1

clk2

clk3

clk4

clk15

clk16

SCK

CONVERT

SLEEP

LOW ICC

DATA OUTPUT

2450 F08

CS

Figure 8. Idle-Low (CPOL = 0) Clock. The 16th SCK Falling Edge Triggers a New Conversion

D15

D14

D13

D12

D2

D1

D0

clk1

clk2

clk3

clk4 clk14

clk15

clk16

SCK

SD0

CONVERT

SLEEP

LOW ICC

DATA OUTPUT

2450 F07

CS

Figure 7. Idle-Low (CPOL = 0) Clock. CS Triggers a New Conversion

相关PDF资料 |

PDF描述 |

|---|---|

| ECM25DCCH | CONN EDGECARD 50POS R/A .156 SLD |

| EBM28DRTI | CONN EDGECARD 56POS DIP .156 SLD |

| ECM25DCCD | CONN EDGECARD 50POS R/A .156 SLD |

| ECM25DCBN | CONN EDGECARD 50POS R/A .156 SLD |

| MLF1608C220M | INDUCTOR MULTILAYER 22UH 0603 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC106R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| DC107 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| DC1073A | 制造商:Linear Technology 功能描述:LT3845EFE DEMO BOARD |

| DC1074A | 功能描述:BOARD DAC LTC2630-12 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:QuikEval™ 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| DC1075A | 功能描述:BOARD COMPANION RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP |

发布紧急采购,3分钟左右您将得到回复。