- 您现在的位置:买卖IC网 > PDF目录17061 > DC846A (Linear Technology)BOARD DELTA SIGMA ADC LTC2447 PDF资料下载

参数资料

| 型号: | DC846A |

| 厂商: | Linear Technology |

| 文件页数: | 28/28页 |

| 文件大小: | 0K |

| 描述: | BOARD DELTA SIGMA ADC LTC2447 |

| 软件下载: | QuikEval System |

| 设计资源: | DC846A Design File DC846A Schematic |

| 标准包装: | 1 |

| 系列: | QuikEval™ |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 8k |

| 数据接口: | MICROWIRE?,串行,SPI? |

| 已用 IC / 零件: | LTC2447 |

| 已供物品: | 板 |

| 相关产品: | LTC2447IUHF#PBF-ND - IC ADC 24BIT 8CH HI SPEED 38QFN LTC2447CUHF#PBF-ND - IC ADC 24BIT 8CH HI SPEED 38QFN LTC2447IUHF#TRPBF-ND - IC ADC 24BIT 8CH HI SPEED 38QFN LTC2447CUHF#TRPBF-ND - IC ADC 24BIT 8CH HI SPEED 38QFN |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页

LTC2446/LTC2447

9

24467fa

convert the bipolar differential input signal, VIN = IN+ –

IN– (where IN+ and IN– are the selected input channels),

from – FS = – 0.5 VREF to +FS = 0.5 VREF where VREF =

REF+ – REF– (REF+ and REF– are the selected references).

Outside this range, the converter indicates the overrange

or the underrange condition using distinct output codes.

MUXOUT/ADCIN

There are two differences between the LTC2446 and the

LTC2447. The first is the RMS noise performance. For a

given OSR, the LTC2447 noise level is approximately

√2

times lower (0.5 effective bits)than that of the LTC2446.

The second difference is the LTC2447 includes MUXOUT/

ADCIN pins. These pins enable an external buffer or gain

block to be inserted between the selected input channel of

the multiplexer and the input to the ADC. Since the buffer

is driven by the output of the multiplexer, only one circuit

is required for all 8 input channels. Additionally, the

transparent calibration feature of the LTC244X family

automatically removes the offset errors of the external

buffer.

In order to achieve optimum performance, the MUXOUT

and ADCIN pins should not be shorted together. In appli-

cations where the MUXOUT and ADCIN need to be shorted

together, the LTC2446 should be used because the

MUXOUT and ADCIN are internally connected for opti-

mum performance.

Output Data Format

The LTC2446/LTC2447 serial output data stream is 32 bits

long. The first 3 bits represent status information indicat-

ing the sign and conversion state. The next 24 bits are the

conversion result, MSB first. The remaining 5 bits are sub

LSBs beyond the 24-bit level that may be included in

averaging or discarded without loss of resolution. In the

case of ultrahigh resolution modes, more than 24 effective

bits of performance are possible (see Table 4). Under

these conditions, sub LSBs are included in the conversion

result and represent useful information beyond the 24-bit

level. The third and fourth bit together are also used to

indicate an underrange condition (the differential input

voltage is below –FS) or an overrange condition (the

differential input voltage is above +FS).

Bit 31 (first output bit) is the end of conversion (EOC)

indicator. This bit is available at the SDO pin during the

conversion and sleep states whenever the CS pin is LOW.

This bit is HIGH during the conversion and goes LOW

when the conversion is complete.

Bit 30 (second output bit) is a dummy bit (DMY) and is

always LOW.

Bit 29 (third output bit) is the conversion result sign indi-

cator (SIG). If VIN is >0, this bit is HIGH. If VIN is <0, this

bit is LOW.

Bit 28 (fourth output bit) is the most significant bit (MSB)

of the result. This bit in conjunction with Bit 29 also

provides the underrange or overrange indication. If both

Bit 29 and Bit 28 are HIGH, the differential input voltage is

above +FS. If both Bit 29 and Bit 28 are LOW, the

differential input voltage is below –FS.

The function of these bits is summarized in Table 1.

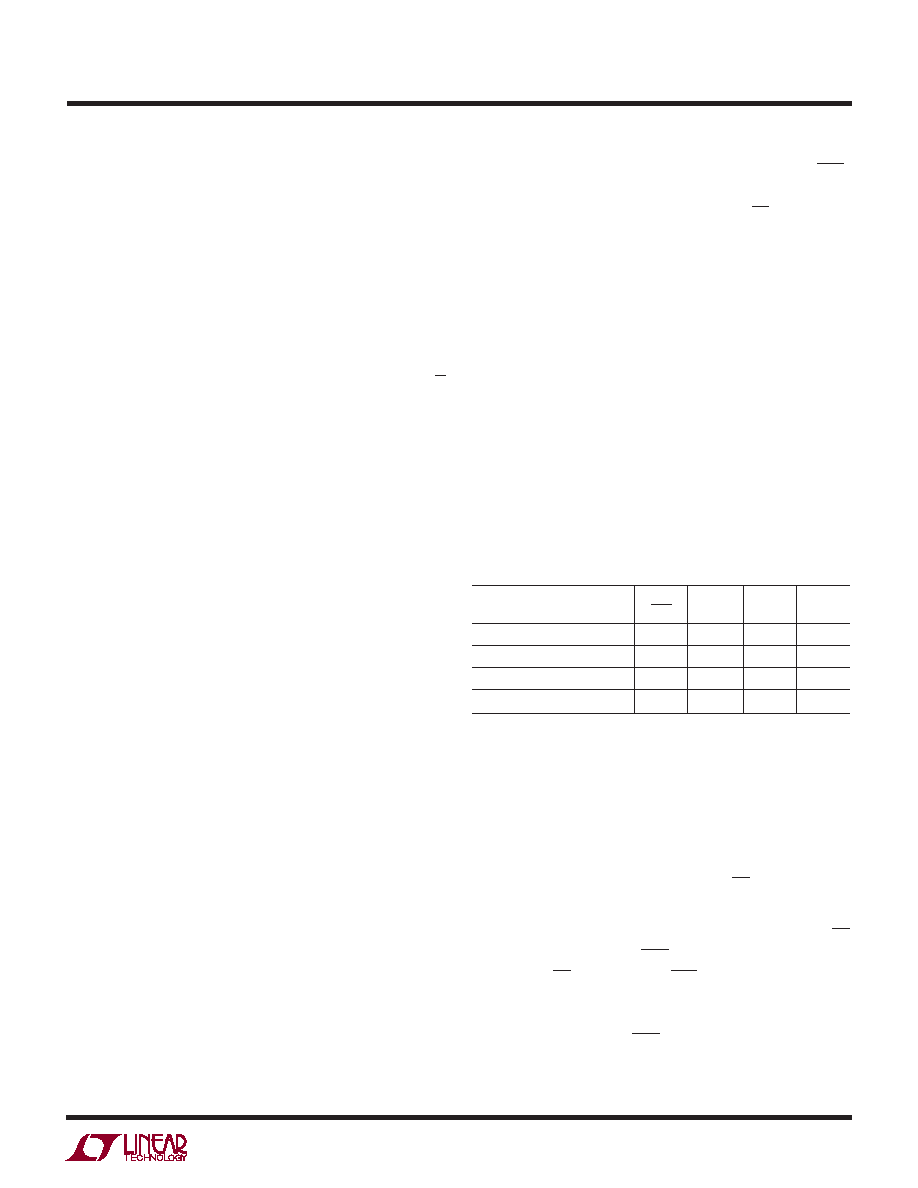

Table 1. LTC2446/LTC2447 Status Bits

BIT 31

BIT 30

BIT 29

BIT 28

INPUT RANGE

EOC

DMY

SIG

MSB

VIN ≥ 0.5 VREF

0011

0V

≤ VIN < 0.5 VREF

0010

–0.5 VREF ≤ VIN < 0V

0001

VIN < – 0.5 VREF

0000

Bits 28-5 are the 24-bit conversion result MSB first.

Bit 5 is the least significant bit (LSB).

Bits 4-0 are sub LSBs below the 24-bit level. Bits 4-0 may

be included in averaging or discarded without loss of

resolution.

Data is shifted out of the SDO pin under control of the serial

clock (SCK), see Figure 3. Whenever CS is HIGH, SDO

remains high impedance and SCK is ignored.

In order to shift the conversion result out of the device, CS

must first be driven LOW. EOC is seen at the SDO pin of the

device once CS is pulled LOW. EOC changes real time from

HIGH to LOW at the completion of a conversion. This

signal may be used as an interrupt for an external

microcontroller. Bit 31 (EOC) can be captured on the first

APPLICATIO S I FOR ATIO

WU

U

相关PDF资料 |

PDF描述 |

|---|---|

| LGN2H680MELZ30 | CAP ALUM 68UF 500V 20% SNAP |

| VE-B20-EY | CONVERTER MOD DC/DC 5V 50W |

| DC956A | BOARD DELTA SIGMA ADC LTC2485 |

| VE-B21-EY | CONVERTER MOD DC/DC 12V 50W |

| DC571A | BOARD DELTA SIGMA ADC LTC2418 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC847A | 功能描述:BOARD DELTA SIGMA ADC LTC2446 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:QuikEval™ 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| DC850 | 制造商:Molex 功能描述: |

| DC852A | 功能描述:BOARD DEMO FOR LTC4354 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| DC8550 | 制造商:DCCOM 制造商全称:Dc Components 功能描述:TECHNICAL SPECIFICATIONS OF PNP EPITAXIAL PLANAR TRANSISTOR |

| DC8550S | 制造商:DCCOM 制造商全称:Dc Components 功能描述:TECHNICAL SPECIFICATIONS OF PNP EPITAXIAL PLANAR TRANSISTOR |

发布紧急采购,3分钟左右您将得到回复。