- 您现在的位置:买卖IC网 > PDF目录381719 > DS1384 (MAXIM INTEGRATED PRODUCTS INC) Watchdog Timekeeping Controller(看门狗计时器芯片) PDF资料下载

参数资料

| 型号: | DS1384 |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | XO, clock |

| 英文描述: | Watchdog Timekeeping Controller(看门狗计时器芯片) |

| 中文描述: | 1 TIMER(S), REAL TIME CLOCK, PQFP44 |

| 封装: | QFP-44 |

| 文件页数: | 7/15页 |

| 文件大小: | 130K |

| 代理商: | DS1384 |

DS1384

062598 7/15

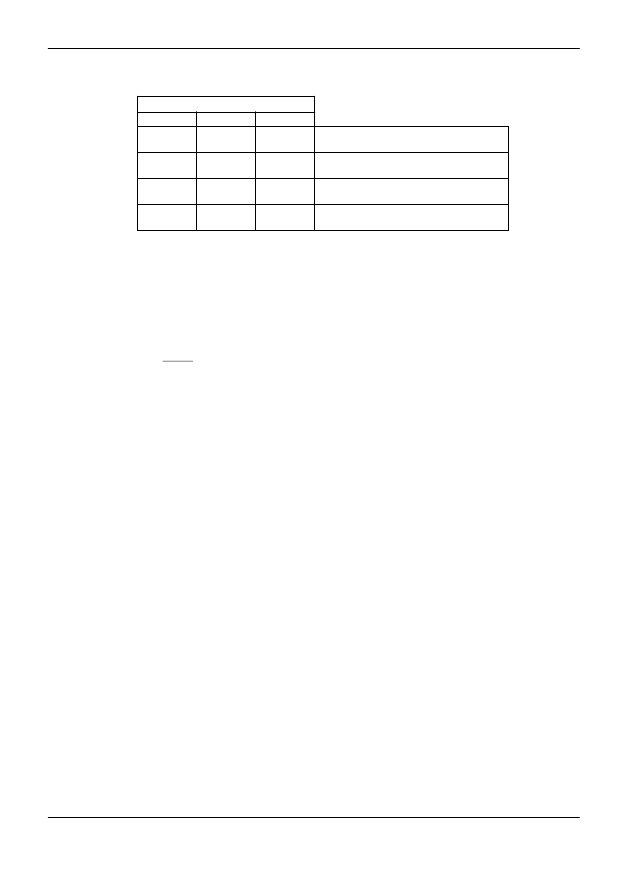

TIME OF DAY ALARM MASK BITS

Figure 3

MINUTES

HOURS

DAYS

1

0

ALARM ONCE PER MINUTE

ALARM WHEN MINUTES MATCH

ALARM WHEN HOURS AND MINUTES MATCH

ALARM WHEN HOURS, MINUTES,

AND DAYS MATCH

1

1

1

1

1

0

0

0

0

0

NOTE: ANY OTHER BIT COMBINATIONS OF MASK BIT SETTINGS PRODUCE ILLOGICAL OPERATION.

REGISTER

TIME OF DAY REGISTERS

Registers 0, 1, 2, 4, 6, 8, 9 and A contain time of day data

in BCD. Ten bits within these eight registers are not

used and will always read zero regardless of how they

are written. Bits 6 and 7 in the Months Register (9) are

binary bits.

When set to logical zero, EOSC (bit 7) enables the real–

time clock oscillator. This bit will normally be turned on

by the user during device initialization. However, the os-

cillator can be turned on and off as necessary by setting

this bit to the appropriate level.

Bit 6 of this same byte controls the square wave output

(pin 24). When set to logical zero, the square wave out-

put pin will output a 1024 Hz square wave signal. When

set to logic one the square wave output pin is in a high

impedance state.

Bit 6 of the Hours Register is defined as the 12– or

24–Hour Select Bit. When set to logic one, the 12–hour

format is selected. In the 12–hour format, bit 5 is the AM/

PM bit with logical one being PM. In the 24–hour mode,

bit 5 is the second 10–hour bit (20–23 hours). The time

of day registers are updated every 0.01 seconds from

the real time clock, except when the TE bit (bit 7 of regis-

ter B) is set low or the clock oscillator is not running.

The preferred method of synchronizing data access to

and from the Watchdog Timekeeper is to access the

Command Register by doing a write cycle to address lo-

cation 0B and setting the TE bit (Transfer Enable bit) to a

logic zero. This will freeze the external time of day regis-

ters at the present recorded time allowing access to oc-

cur without danger of simultaneous update. When the

watch registers have been read or written a second

write cycle to location 0B, setting the TE bit to a logic

one, will put the time of day registers back to being up-

dated every 0.01 second. No time is lost in the real time

clock because the internal copy of the time of day regis-

ter buffers are continually incremented while the exter-

nal memory registers are frozen. An alternate method of

reading and writing the time of day registers is to ignore

synchronization. However, any single read may give er-

roneous data as the real time clock may be in the pro-

cess of updating the external memory registers as data

is being read.

The internal copies of seconds through years are in-

cremented and Time of Day Alarm is checked during the

period that hundredths of seconds reads 99 and are

transferred to the external register when hundredths of

seconds roll from 99 to 00. A way of making sure data is

valid is to do multiple reads and compare. Writing the

registers can also produce erroneous results for the

same reasons. A way of making sure that the write cycle

has caused proper update is to do read verifies and re-

execute the write cycle if data is not correct. While the

possibility of erroneous results from reads and write

cycles has been stated, it is worth noting that the proba-

bility of an incorrect result is kept to a minimum due to

the redundant structure of the Watchdog Timekeeper.

TIME OF DAY ALARM REGISTERS

Registers 3, 5, and 7 contain the time of day alarm regis-

ters. Bits 3, 4, 5, and 6 of register 7 will always read zero

regardless of how they are written. Bit 7 of registers 3, 5,

and 7 are mask bits (Figure 3). When all of the mask bits

are logical zero, a time of day alarm will only occur when

registers 2, 4, and 6 match the values stored in registers

3, 5, and 7. An alarm will be generated every day when

bit 7 of register 7 is set to a logical one. Similarly, an

alarm is generated every hour when bit 7 of registers 7

相关PDF资料 |

PDF描述 |

|---|---|

| DS1386 | Nonvolatile Static RAM with a Full Function Real Time Clock (RTC),(带完整功能的实时时钟静态RAM) |

| DS1386P | RAMified Watchdog Timekeeper(带完整功能的实时时钟静态RAM) |

| DS1388Z-3 | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| DS1390-DS1393 | RIBBON CABLE, 34WAY, PER M; Cores, No. of:34; Conductor make-up:7/36AWG; Wire size, AWG:28AWG; Impedance:119R; Pitch:1.27mm; Voltage rating, AC:50V; Colour:Grey; Capacitance:70.5pF/m; Approval Bodies:UL; Approval category:Style RoHS Compliant: Yes |

| DS1390U-18 | RIBBON CABLE, 40WAY, PER M; Cores, No. of:40; Conductor make-up:7/36AWG; Wire size, AWG:28AWG; Impedance:119R; Pitch:1.27mm; Voltage rating, AC:50V; Colour:Grey; Capacitance:70.5pF/m; Approval Bodies:UL; Approval category:Style RoHS Compliant: Yes |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1384FP | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Watchdog Timekeeping Controller |

| DS1384FP-12 | 功能描述:IC CTRLR RTC WDOG 120NS 44-MQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 实时时钟 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 类型:时钟/日历 特点:警报器,闰年,SRAM 存储容量:- 时间格式:HH:MM:SS(12/24 小时) 数据格式:YY-MM-DD-dd 接口:SPI 电源电压:2 V ~ 5.5 V 电压 - 电源,电池:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WDFN 裸露焊盘 供应商设备封装:8-TDFN EP 包装:管件 |

| DS1384FP-12+ | 功能描述:实时时钟 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| DS1384FP-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Real-Time Clock |

| DS1384T-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Real-Time Clock |

发布紧急采购,3分钟左右您将得到回复。