参数资料

| 型号: | DS2156DK |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 6/21页 |

| 文件大小: | 0K |

| 描述: | KIT DESIGN FOR DS2156 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 主要目的: | 电信,线路接口单元(LIU) |

| 已用 IC / 零件: | DS2156 |

�� �

�

�

�DS2155DK/DS2156DK� T1/E1/J1� Single-Chip� Transceiver� Design� Kit� Daughter� Cards�

�CPLD� Register� Map�

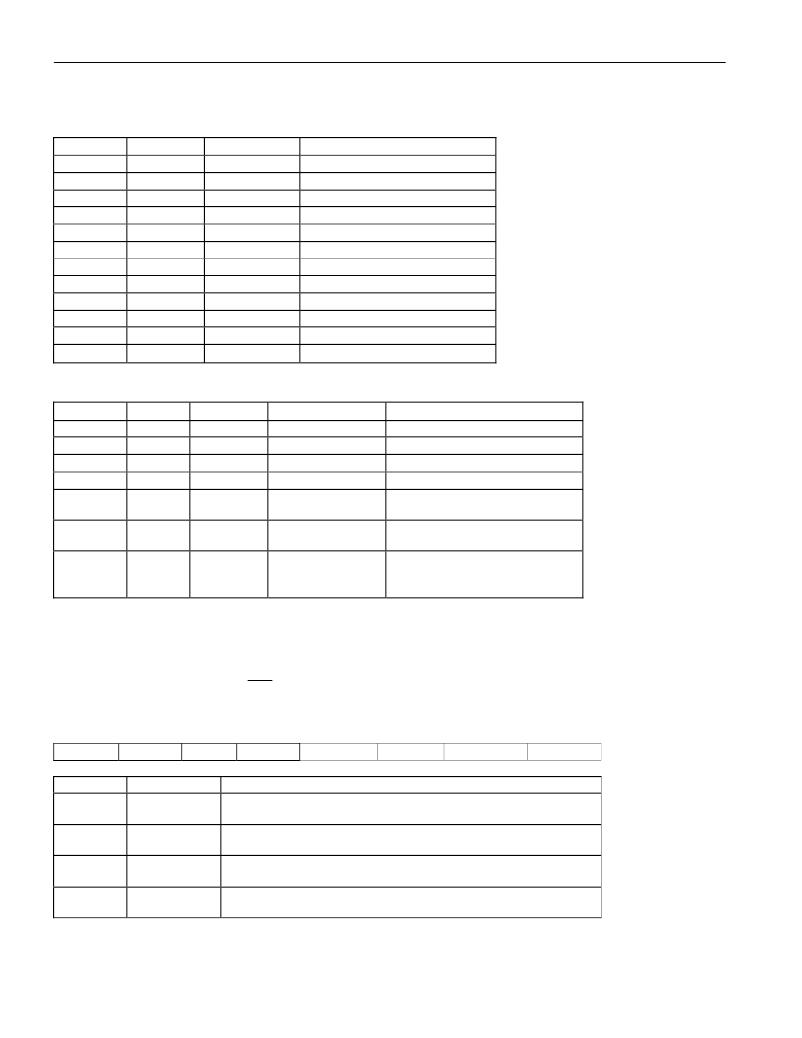

�Table� 2.� CPLD� Register� Map�

�OFFSET�

�0X0000�

�0X0002�

�0X0003�

�0X0004�

�0X0005�

�0X0006�

�0X0007�

�0X0011�

�0X0012�

�0X0013�

�0X0014�

�0X0015�

�NAME�

�BID�

�XBIDH�

�XBIDM�

�XBIDL�

�BREV�

�AREV�

�PREV�

�SWITCH1�

�SWITCH2�

�SWITCH3�

�SWITCH4�

�LEVELS�

�TYPE�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Write�

�Read-Write�

�Read-Write�

�Read-Write�

�Read-Write�

�DESCRIPTION�

�Board� ID�

�High-Nibble� Extended� Board� ID�

�Middle-Nibble� Extended� Board� ID�

�Low-Nibble� Extended� Board� ID�

�Board� FAB� Revision�

�Board� Assembly� Revision�

�PLD� Revision�

�Pin� to� 1.544MHz�

�Pin� to� 2.048MHz�

�Pin-to-Pin� Connect�

�Pin-to-Pin� Connect�

�Set� Level� On� Pin� 1� =� 3.3V�

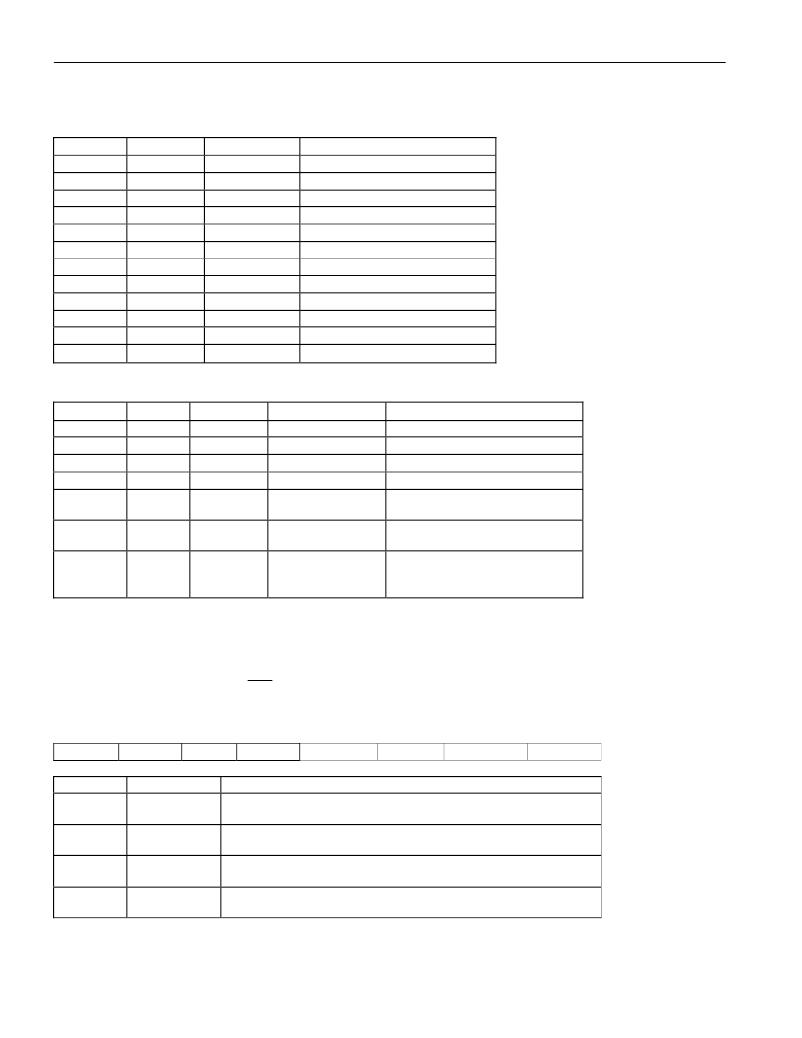

�ID� Registers�

�OFFSET�

�0X0000�

�0X0002�

�0X0003�

�0X0004�

�0X0005�

�0X0006�

�NAME�

�BID�

�XBIDH�

�XBIDM�

�XBIDL�

�BREV�

�AREV�

�TYPE�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�Read-Only�

�VALUE�

�0xD�

�0x0�

�0x0�

�0x5�

�Displays� current�

�FAB� revision�

�Displays� current�

�assembly� revision�

�DESCRIPTION�

�Board� ID�

�High-Nibble� Extended� Board� ID�

�Middle-Nibble� Extended� Board� ID�

�Low-Nibble� Extended� Board� ID�

�Board� FAB� Revision�

�Board� Assembly� Revision�

�Displays� current�

�0X0007�

�PREV�

�Read-Only�

�PLD� firmware�

�PLD� Revision�

�revision�

�Control� Registers�

�The� control� registers� are� used� primarily� to� control� several� banks� of� FET� switches� that� route� clocks� and� backplane�

�signals.� Please� note� that� certain� register� settings� cause� line� contention,� e.g.,� setting� SWITCH1.4� and� SWITCH2.4�

�both� to� 0� would� drive� MCLK� with� both� 1.544MHz� and� 2.048MHz.�

�SWITCH1:� PIN� TO� 1.544MHz� (OFFSET� =� 0x0011)� INITIAL� VALUE� =� 0xF�

�(MSB)�

�(LSB)�

�—�

�—�

�—�

�—�

�MCLK�

�TCLK�

�RSYSCLK�

�TSYSCLK�

�NAME�

�MCLK�

�TCLK�

�RSYSCLK�

�TSYSCLK�

�POSITION�

�SWITCH1.3�

�SWITCH1.2�

�SWITCH1.1�

�SWITCH1.0�

�FUNCTION�

�0� =� Connect� MCLK� to� the� 1.544MHz� clock�

�1� =� Open� Switch� 1.4�

�0� =� Connect� TCLK� to� the� 1.544MHz� clock�

�1� =� Open� Switch� 1.3�

�0� =� Connect� RSYSCLK� to� the� 1.544MHz� clock�

�1� =� Open� Switch� 1.2�

�0� =� Connect� TSYSCLK� to� the� 1.544MHz� clock�

�1� =� Open� Switch� 1.1�

�6� of� 21�

�相关PDF资料 |

PDF描述 |

|---|---|

| DS21Q348DK | KIT DESIGN FOR DS21Q348 |

| DS21Q55DK | KIT DESIGN FOR DS21Q55 |

| DS2436K | KIT DEMO BATT ID/MON CHIP DS2436 |

| DS2438K | KIT DEMO SMART BATT MON DS2438 |

| DS26303DK | KIT DESIGN FOR DS26303 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2156G | 制造商:Maxim Integrated Products 功能描述:DS2156 T1/E1/J1 SCT+UTOPIA 100BGA - Trays |

| DS2156G+ | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:T1/E1/J1 Single-Chip Transceiver TDM/UTOPIA II Interface |

| DS2156GN | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:T1/E1/J1 Single-Chip Transceiver TDM/UTOPIA II Interface |

| DS2156GN+ | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:T1/E1/J1 Single-Chip Transceiver TDM/UTOPIA II Interface |

| DS2156L | 功能描述:网络控制器与处理器 IC T1/E1/J1 Transceiver TDM/UTOPIA II Intrfc RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。