- 您现在的位置:买卖IC网 > Datasheet目录322 > DS2423D/T&R (Maxim Integrated)IC SRAM 4KBIT 6FCHIP Datasheet资料下载

参数资料

| 型号: | DS2423D/T&R |

| 厂商: | Maxim Integrated |

| 文件页数: | 19/26页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 4KBIT 6FCHIP |

| 标准包装: | 10,000 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM |

| 存储容量: | 4K (256 x 16) |

| 接口: | 1 线 串行 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 6-XBGA,FCBGA |

| 供应商设备封装: | 6-覆晶(2.82x2.54) |

| 包装: | 带卷 (TR) |

�� �

�

�

�DS2423�

�1-WIRE� SIGNALING�

�The� DS2423� requires� strict� protocols� to� ensure� data� integrity.� The� protocol� consists� of� four� types� of�

�signaling� on� one� line:� Reset� Sequence� with� Reset� Pulse� and� Presence� Pulse,� Write� 0,� Write� 1� and� Read�

�Data.� The� bus� master� initiates� all� these� signals� except� Presence� Pulse.� The� DS2423� can� communicate� at�

�two� different� speeds,� regular� speed� and� Overdrive� speed.� If� not� explicitly� set� into� the� Overdrive� mode,� the�

�DS2423� will� communicate� at� regular� speed.� While� in� Overdrive� mode� the� fast� timing� applies� to� all�

�waveforms.�

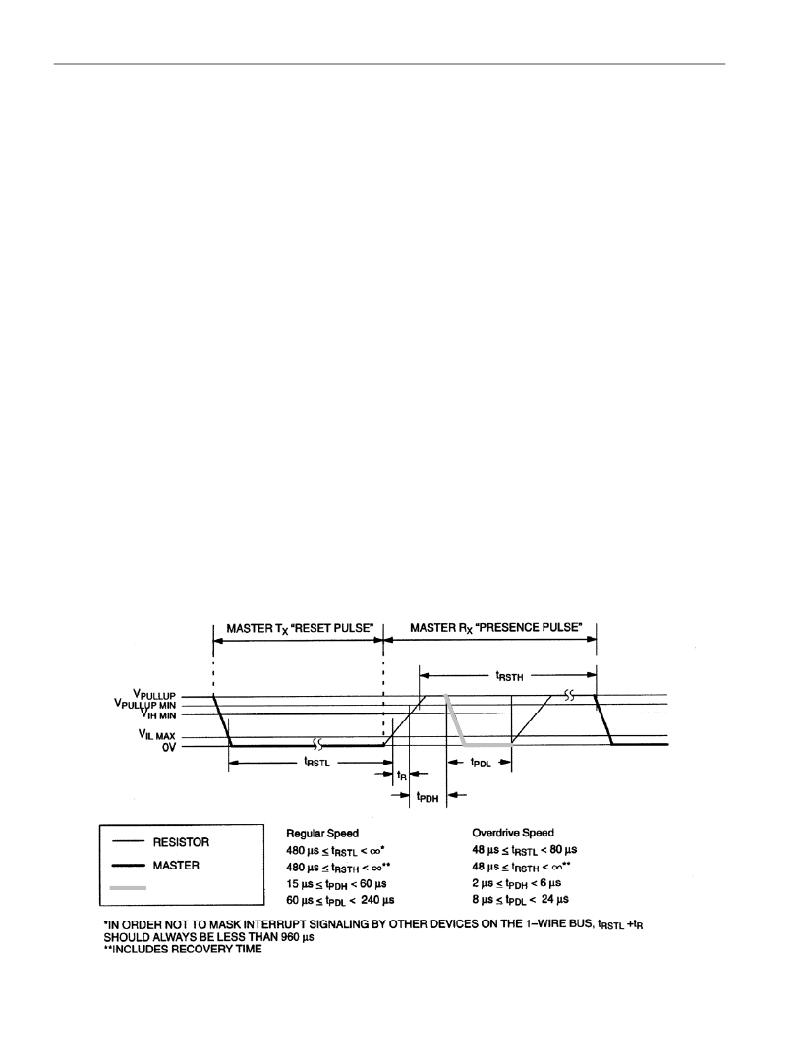

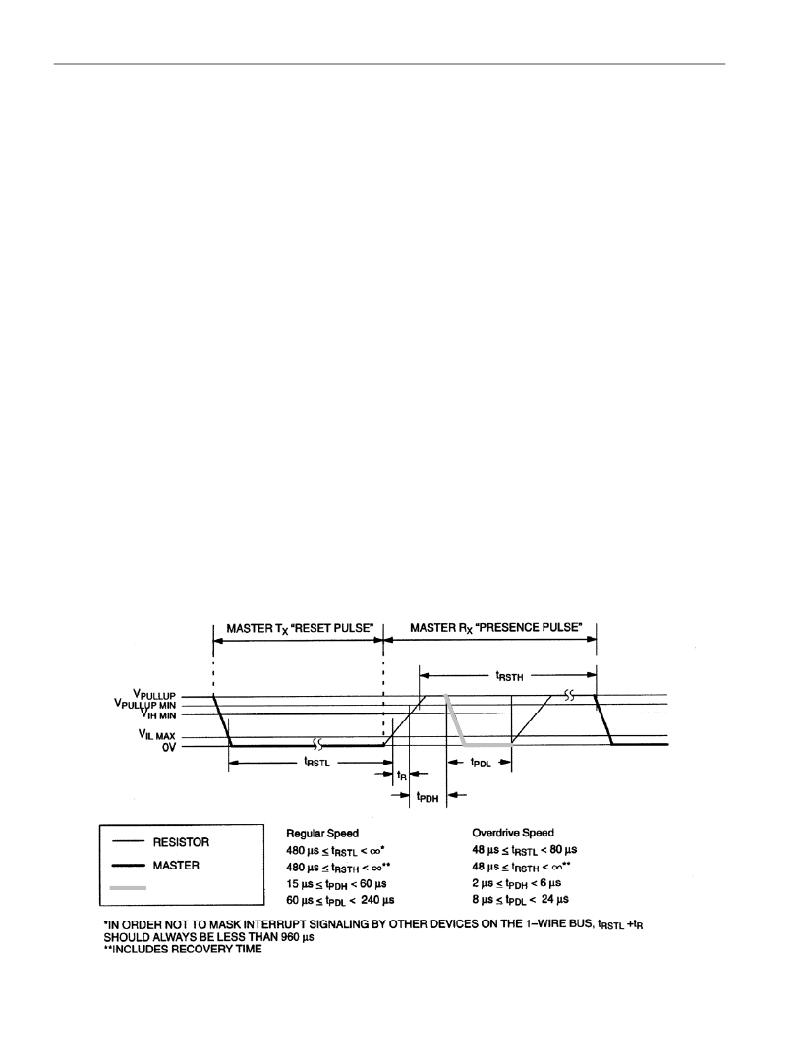

�The� initialization� sequence� required� to� begin� any� communication� with� the� DS2423� is� shown� in� Figure� 10.�

�A� Reset� Pulse� followed� by� a� Presence� Pulse� indicates� the� DS2423� is� ready� to� send� or� receive� data� given�

�the� correct� ROM� command� and� memory� function� command.� The� bus� master� transmits� (TX)� a� Reset�

�Pulse� (t� RSTL� ,� minimum� 480� μs� at� regular� speed,� 48� μs� at� Overdrive� speed).� The� bus� master� then� releases�

�the� line� and� goes� into� receive� mode� (RX).� The� 1-Wire� bus� is� pulled� to� a� high� state� via� the� pullup� resistor.�

�After� detecting� the� rising� edge� on� the� data� pin,� the� DS2423� waits� (t� PDH� ,� 15-60μs� at� regular� speed,� 2-6μs� at�

�Overdrive� speed)� and� then� transmits� the� Presence� Pulse� (t� PDL� ,� 60-240μs� at� regular� speed,� 8-24μs� at�

�Overdrive� speed).�

�A� Reset� Pulse� of� 480μs� or� longer� will� exit� the� Overdrive� mode� returning� the� device� to� regular� speed.� If�

�the� DS2423� is� in� Overdrive� mode� and� the� Reset� Pulse� is� no� longer� than� 80μs� the� device� will� remain� in�

�Overdrive� mode.�

�Read/Write� Time� Slots�

�The� definitions� of� write� and� read� time� slots� are� illustrated� in� Figure� 11.� All� time� slots� are� initiated� by� the�

�master� driving� the� data� line� low.� The� falling� edge� of� the� data� line� synchronizes� the� DS2423� to� the� master�

�by� triggering� a� delay� circuit� in� the� DS2423.� During� write� time� slots,� the� delay� circuit� determines� when� the�

�DS2423� will� sample� the� data� line.� For� a� read� data� time� slot,� if� a� “0”� is� to� be� transmitted,� the� delay� circuit�

�determines� how� long� the� DS2423� will� hold� the� data� line� low� overriding� the� 1� generated� by� the� master.� If�

�the� data� bit� is� a� “1”,� the� device� will� leave� the� read� data� time� slot� unchanged.�

�INITIALIZATION� PROCEDURE� “RESET� AND� PRESENCE� PULSES”� Figure� 10�

�DS2423�

�19� of� 25�

�相关PDF资料 |

PDF描述 |

|---|---|

| DS2430AP+T&R | IC EEPROM 256BIT 6TSOC |

| DS2431GA+U | IC EEPROM 1024BIT 2SFN |

| DS2433X-S#T | IC EEPROM 4KBIT 6FCHIP |

| DS2433X-Z01 | IC EEPROM 4KBIT 6FCHIP |

| DS24B33G+T&R | IC EEPROM 4KBIT 2SFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2423MRAB0 | 制造商:Thomas & Betts 功能描述:300A,NLT,3P4W,MG,423,3P480V |

| DS2423P | 功能描述:静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| DS2423P/R | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4kbit 1-Wire RAM with Counter |

| DS2423P/T | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4kbit 1-Wire RAM with Counter |

| DS2423P/T&R | 功能描述:静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。