- 您现在的位置:买卖IC网 > PDF目录2067 > DS2450S+T&R (Maxim Integrated Products)IC CONVERTER A/D QUAD 1-W 8-SOIC PDF资料下载

参数资料

| 型号: | DS2450S+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 10/25页 |

| 文件大小: | 0K |

| 描述: | IC CONVERTER A/D QUAD 1-W 8-SOIC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 产品变化通告: | Product Discontinuation 27/Jul/12 |

| 标准包装: | 2,000 |

| 位数: | 16 |

| 采样率(每秒): | 1k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 4 个单端,单极 |

DS2450

18 of 24

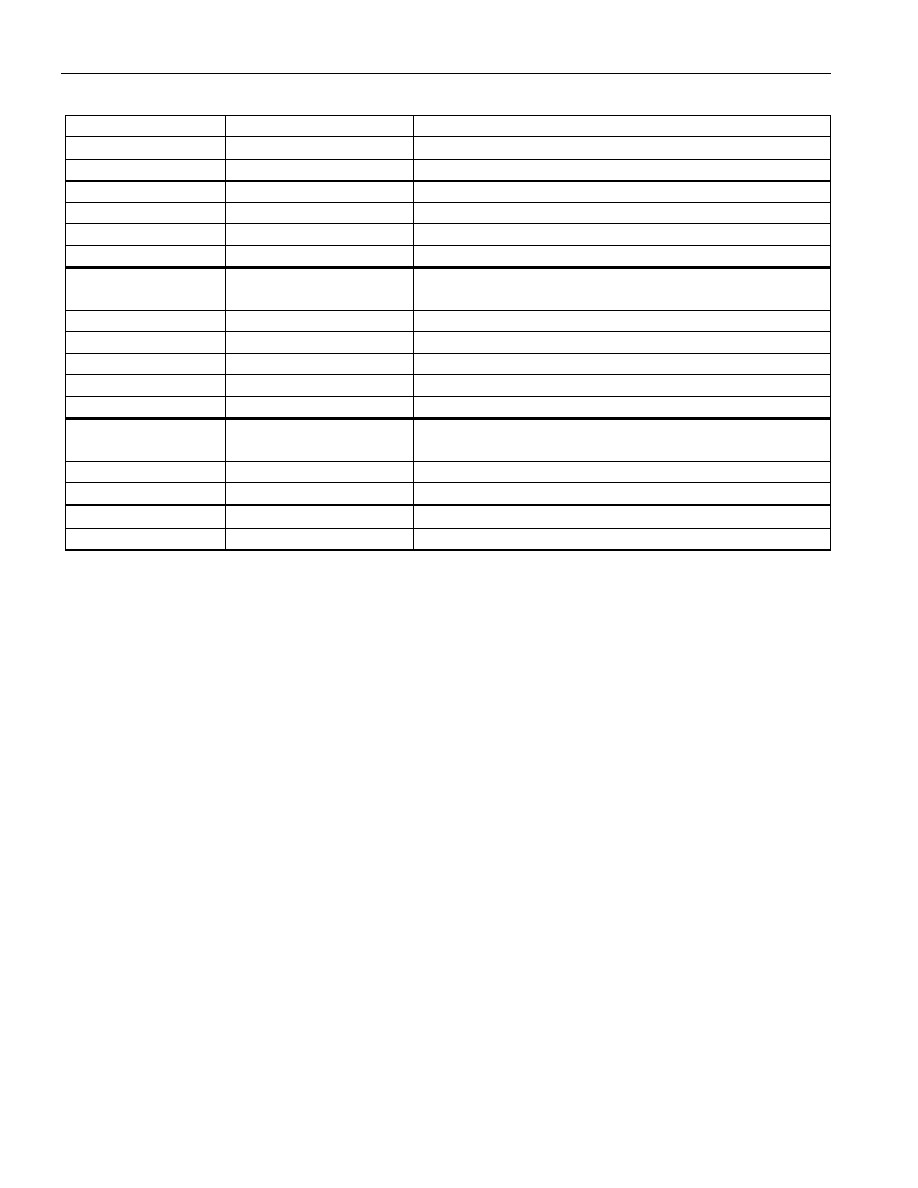

USAGE EXAMPLE (control channel A and channel B outputs)

MASTER MODE

DATA (LSB FIRST) COMMENTS

TX

Reset

Reset Pulse (480 - 960 μs)

RX

Presence

Presence Pulse

TX

CCh

Issue “Skip ROM” Command

TX

55h

Issue “Write Memory” Command

TX

08h

TA1, beginning address

TX

00h

TA2, address = 0008h

TX

80h if AFL = 1 / C0h if

AFL = 0

data byte (address 0008)

CH-A

RX

<CRC16>

CRC of command, address, data byte

RX

<data byte>

read-back for simple verification

TX

00h

next data byte (address 0009h)*

RX

<CRC16>

CRC of address, data byte

RX

00h

read-back for simple verification

TX

80h if AFH = 1 / C0h if

AFH = 0

data byte (address 000A)

CH-B

RX

<CRC16>

CRC of address, data byte

RX

<data byte>

read-back for simple verification

TX

Reset

Reset Pulse (480 - 960 μs)

RX

Presence

Presence Pulse

*In a multi-drop environment it takes less time to perform a non-changing write cycle rather than

skipping a byte.

1-WIRE SIGNALING

The DS2450 requires strict protocols to ensure data integrity. The protocol consists of four types of

signaling on one line: reset sequence with reset pulse and presence pulse, Write 0, Write 1 and Read Data.

All these signals except presence pulse are initiated by the bus master. The DS2450 can communicate at

two different speeds, regular speed and Overdrive Speed. If not explicitly set into the Overdrive mode,

the DS2450 will communicate at regular speed. While in Overdrive mode the fast timing applies to all

wave forms.

The initialization sequence required to begin any communication with the DS2450 is shown in Figure 10.

A Reset Pulse followed by a Presence Pulse indicates the DS2450 is ready to send or receive data given

the correct ROM command and memory function command. The bus master transmits (TX) a reset pulse

(tRSTL, minimum 480 μs at regular speed, 48 μs at Overdrive Speed). The bus master then releases the

line and goes into receive mode (RX). The 1-Wire bus is pulled to a high state via the pullup resistor.

After detecting the rising edge on the data pin, the DS2450 waits (tPDH,15-60 μs at regular speed, 2-6 μs

at Overdrive speed) and then transmits the Presence Pulse (tPDL, 60-240 μs at regular speed, 8-24 μs at

Overdrive Speed).

A Reset Pulse of 480 μs or longer will exit the Overdrive Mode returning the device to regular speed. If

the DS2450 is in Overdrive Mode and the Reset Pulse is no longer than 80 μs the device will remain in

Overdrive Mode.

相关PDF资料 |

PDF描述 |

|---|---|

| DS3508E+ | IC GAMMA BUFFER 8CH 20-TSSOP |

| DS3510T+ | IC I2C GAMMA/VCOM BUFF 48-TQFN |

| DS3514T+T&R | IC I2C GAMMA/VCOM BUFF 48-TQFN |

| EL1881CS-T13 | IC VIDEO SYNC SEPARATOR 8-SOIC |

| EL1883IS-T13 | IC VID SYNC SEPARATOR HORZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS245CEDX | 制造商:CUTLER HAMMER/EATON 功能描述: 制造商:Eaton Corporation 功能描述: 制造商:Eaton Corporation 功能描述:RWD |

| DS246 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| DS2460 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:SHA-1 Coprocessor with EEPROM |

| DS2460+ | 制造商:Maxim Integrated Products 功能描述: |

| DS2460S | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:SHA-1 Coprocessor with EEPROM |

发布紧急采购,3分钟左右您将得到回复。