参数资料

| 型号: | DS24B33S+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 17/23页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 4KBIT 8SOIC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,000 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 4K (256 x 16) |

| 接口: | 1 线 |

| 电源电压: | 2.8 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SO |

| 包装: | 带卷 (TR) |

�� �

�

�

�DS24B33�

�1-Wire� 4Kb� EEPROM�

�1-Wire� Signaling�

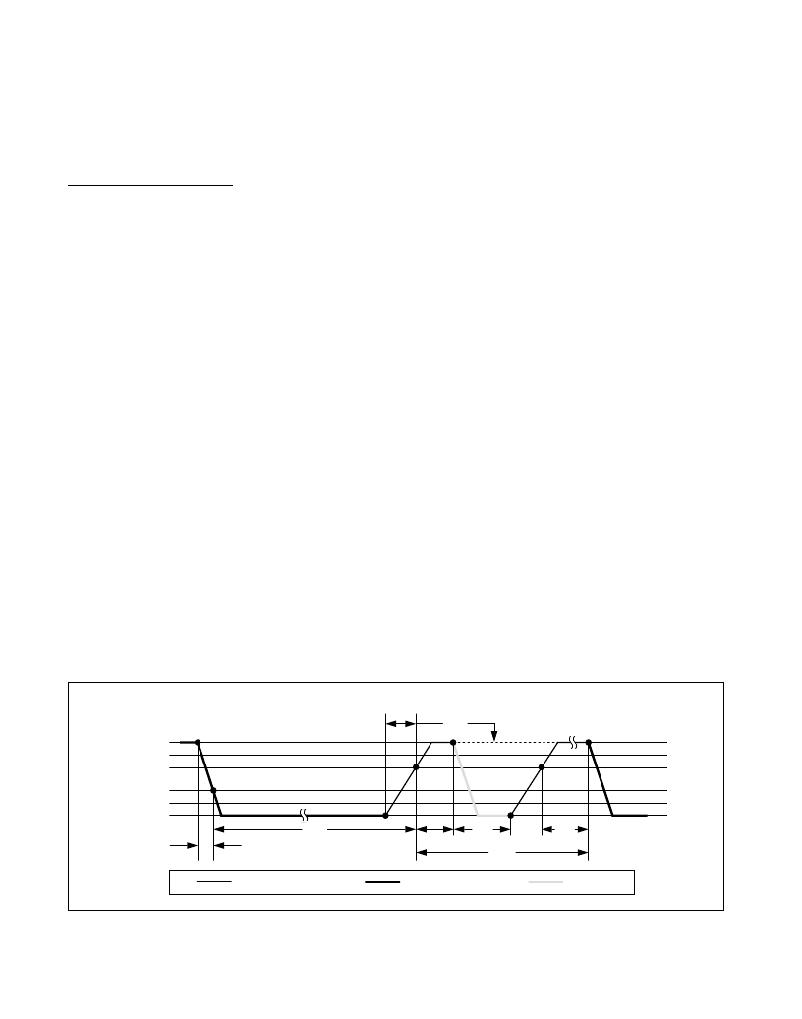

�The� DS24B33� requires� strict� protocols� to� ensure� data�

�integrity.� The� protocol� consists� of� four� types� of� signaling�

�on� one� line:� reset� sequence� with� reset� pulse� and� pres-�

�ence� pulse,� write-zero,� write-one,� and� read-data.�

�Except� for� the� presence� pulse,� the� bus� master� initiates�

�all� falling� edges.� The� DS24B33� can� communicate� at�

�two� different� speeds:� standard� speed� and� overdrive�

�speed.� If� not� explicitly� set� into� the� overdrive� mode,� the�

�DS24B33� communicates� at� standard� speed.� While� in�

�overdrive� mode� the� fast� timing� applies� to� all� waveforms.�

�To� get� from� idle� to� active,� the� voltage� on� the� 1-Wire� line�

�needs� to� fall� from� V� PUP� below� the� threshold� V� TL� .� To� get�

�from� active� to� idle,� the� voltage� needs� to� rise� from�

�V� ILMAX� past� the� threshold� V� TH� .� The� time� it� takes� for� the�

�voltage� to� make� this� rise� is� seen� in� Figure� 10� as� ε� ,� and�

�its� duration� depends� on� the� pullup� resistor� (R� PUP� )� used�

�and� the� capacitance� of� the� 1-Wire� network� attached.�

�The� voltage� V� ILMAX� is� relevant� for� the� DS24B33� when�

�determining� a� logical� level,� not� triggering� any� events.�

�Figure� 10� shows� the� initialization� sequence� required� to�

�begin� any� communication� with� the� DS24B33.� A� reset�

�pulse� followed� by� a� presence� pulse� indicates� that� the�

�DS24B33� is� ready� to� receive� data,� given� the� correct�

�ROM� and� memory� function� command.� If� the� bus� master�

�uses� slew-rate� control� on� the� falling� edge,� it� must� pull�

�down� the� line� for� t� RSTL� +� t� F� to� compensate� for� the� edge.�

�A� t� RSTL� duration� of� 480μs� or� longer� exits� the� overdrive�

�mode,� returning� the� device� to� standard� speed.� If� the�

�DS24B33� is� in� overdrive� mode� and� t� RSTL� is� no� longer�

�than� 80μs,� the� device� remains� in� overdrive� mode.� If� the�

�device� is� in� overdrive� mode� and� t� RSTL� is� between� 80μs�

�and� 480μs,� the� device� resets,� but� the� communication�

�speed� is� undetermined.�

�MASTER� Tx� "RESET� PULSE"�

�V� PUP�

�V� IHMASTER�

�V� TH�

�V� TL�

�V� ILMAX�

�ε�

�After� the� bus� master� has� released� the� line� it� goes� into�

�receive� mode.� Now� the� 1-Wire� bus� is� pulled� to� V� PUP�

�through� the� pullup� resistor,� or� in� case� of� a� DS2482-x00�

�or� DS2480B� driver,� by� active� circuitry.� When� the� thresh-�

�old� V� TH� is� crossed,� the� DS24B33� waits� for� t� PDH� and�

�then� transmits� a� presence� pulse� by� pulling� the� line� low�

�for� t� PDL� .� To� detect� a� presence� pulse,� the� master� must�

�test� the� logical� state� of� the� 1-Wire� line� at� t� MSP� .�

�The� t� RSTH� window� must� be� at� least� the� sum� of� t� PDHMAX� ,�

�t� PDLMAX� ,� and� t� RECMIN� .� Immediately� after� t� RSTH� is�

�expired,� the� DS24B33� is� ready� for� data� communication.�

�In� a� mixed� population� network,� t� RSTH� should� be� extend-�

�ed� to� minimum� 480μs� at� standard� speed� and� 48μs� at�

�overdrive� speed� to� accommodate� other� 1-Wire� devices.�

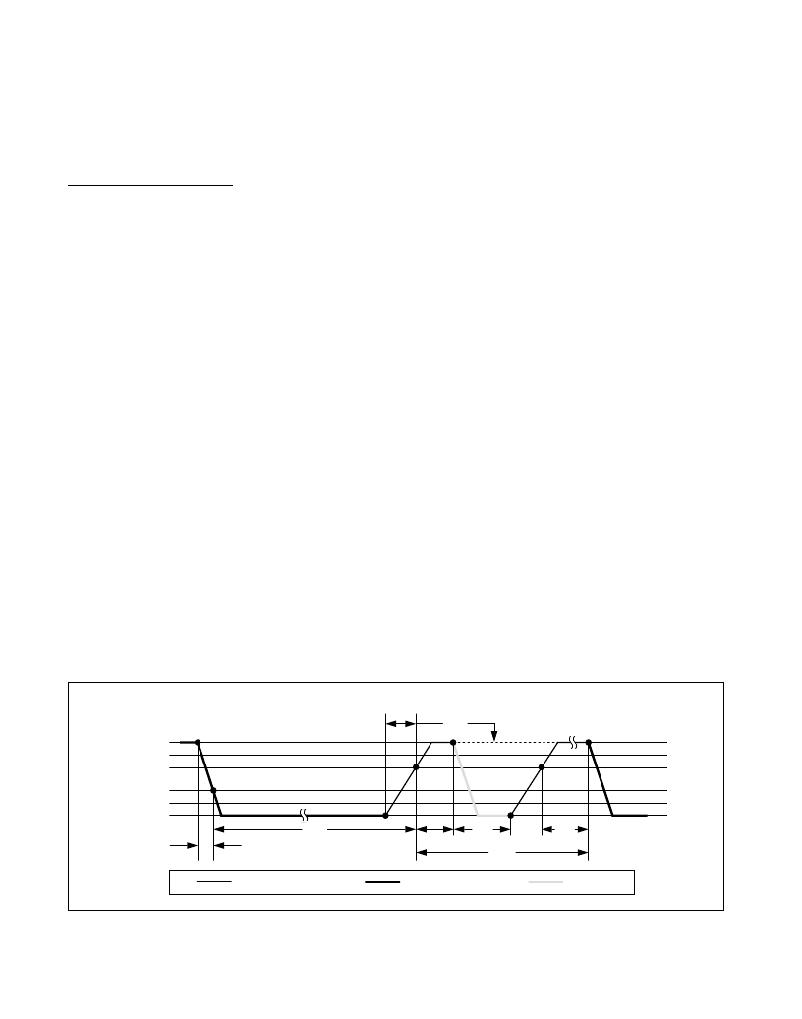

�Read/Write� Time� Slots�

�Data� communication� with� the� DS24B33� takes� place� in�

�time� slots,� which� carry� a� single� bit� each.� Write� time� slots�

�transport� data� from� bus� master� to� slave.� Read� time�

�slots� transfer� data� from� slave� to� master.� Figure� 11� illus-�

�trates� the� definitions� of� the� write� and� read� time� slots.�

�All� communication� begins� with� the� master� pulling� the�

�data� line� low.� As� the� voltage� on� the� 1-Wire� line� falls�

�below� the� threshold� V� TL� ,� the� DS24B33� starts� its� internal�

�timing� generator� that� determines� when� the� data� line� is�

�sampled� during� a� write� time� slot� and� how� long� data� is�

�valid� during� a� read� time� slot.�

�Master-to-Slave�

�For� a� write-one� time� slot,� the� voltage� on� the� data� line�

�must� have� crossed� the� V� TH� threshold� before� the� write-�

�one� low� time� t� W1LMAX� is� expired.� For� a� write-zero� time�

�slot,� the� voltage� on� the� data� line� must� stay� below� the�

�V� TH� threshold� until� the� write-zero� low� time� t� W0LMIN� is�

�expired.� For� the� most� reliable� communication,� the�

�MASTER� Rx� "PRESENCE� PULSE"�

�t� MSP�

�0V�

�t� RSTL�

�t� PDH�

�t� PDL�

�t� REC�

�t� F�

�t� RSTH�

�RESISTOR�

�Figure� 10.� Initialization� Procedure:� Reset� and� Presence� Pulse�

�Maxim� Integrated�

�MASTER�

�DS24B33�

�17�

�相关PDF资料 |

PDF描述 |

|---|---|

| DS24B33Q+T&R | IC EEPROM 4KBIT 6TDFN-EP |

| DS24B33+T&R | IC EEPROM 4KBIT TO92-3 |

| 395-026-521-802 | CARD EDGE 26POS DL .100X.200 BLK |

| 395-026-521-801 | CARD EDGE 26POS DL .100X.200 BLK |

| 395-026-521-204 | CARD EDGE 26POS DL .100X.200 BLK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS24L65P+T | 制造商:Maxim Integrated Products 功能描述:SHA256 1.8V COPROCESSOR WITH 1-WIRE MASTER T&R - Tape and Reel |

| DS25 | 制造商:DIGIMESS 功能描述:OSCILLOSCOPE DSO 25MHZ 制造商:DIGIMESS 功能描述:OSCILLOSCOPE, DSO, 25MHZ |

| DS2500PE-3 | 功能描述:线性和开关式电源 12V output 2500W 3.3V RoHS:否 制造商:TDK-Lambda 产品:Switching Supplies 开放式框架/封闭式:Enclosed 输出功率额定值:800 W 输入电压:85 VAC to 265 VAC 输出端数量:1 输出电压(通道 1):20 V 输出电流(通道 1):40 A 商用/医用: 输出电压(通道 2): 输出电流(通道 2): 安装风格:Rack 长度: 宽度: 高度: |

| DS2501 | 功能描述:低压差稳压器 - LDO RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| DS2501MP000 | 制造商:Thomas & Betts 功能描述:200 AMP PLUG 4P5W 501, 220/380V-50 |

发布紧急采购,3分钟左右您将得到回复。