参数资料

| 型号: | DS2505P+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 22/24页 |

| 文件大小: | 0K |

| 描述: | IC OTP 16KBIT 6TSOC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 4,000 |

| 格式 - 存储器: | EPROMs |

| 存储器类型: | EPROM OTP |

| 存储容量: | 16K(16K x 1) |

| 接口: | 1 线 串行 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 6-LSOJ |

| 供应商设备封装: | 6-TSOC |

| 包装: | 带卷 (TR) |

�� ��

��

��

��DS2505�

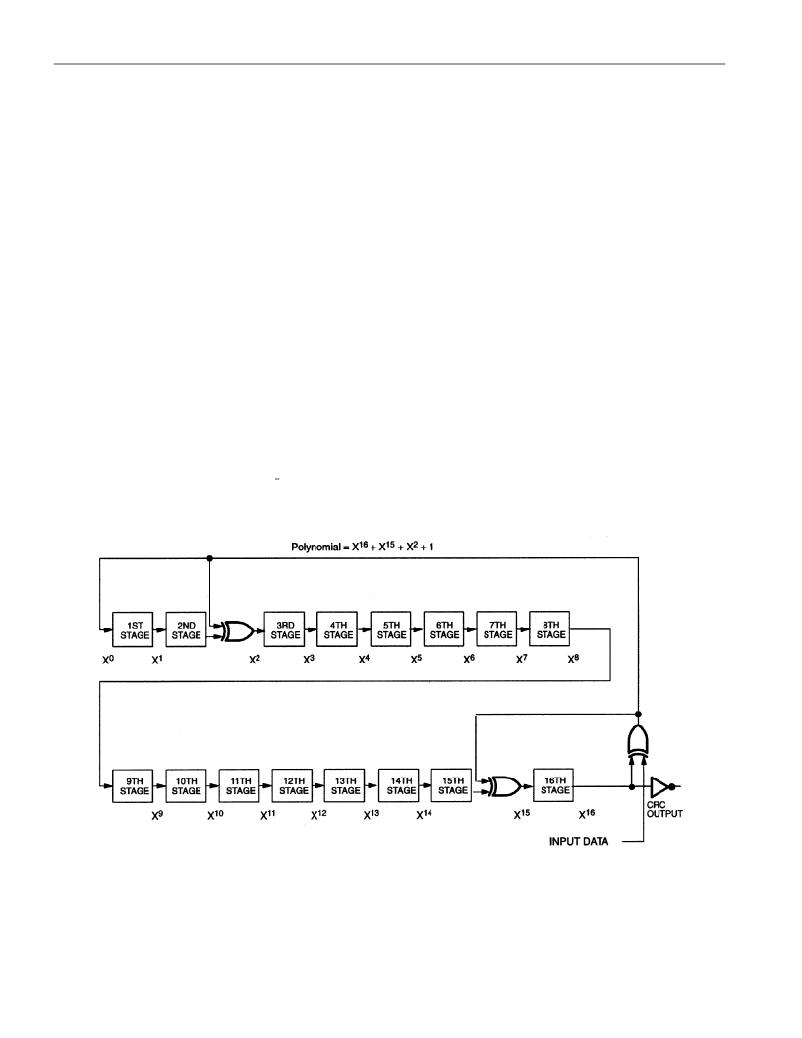

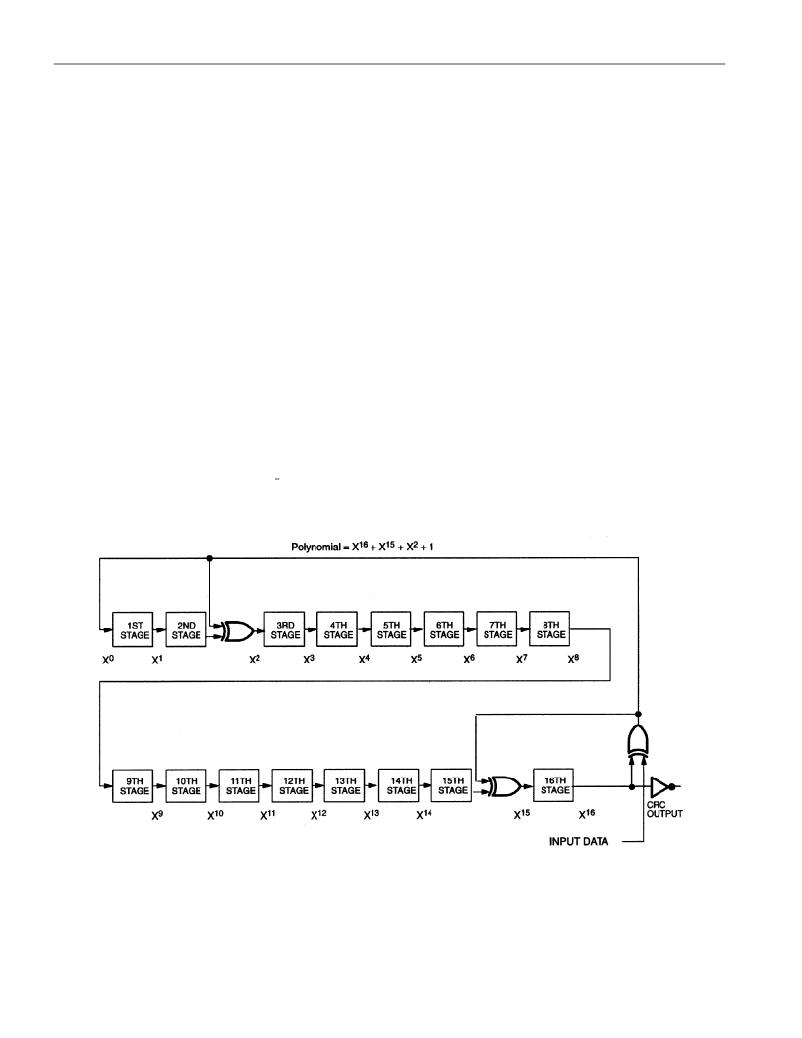

�When� reading� the� data� memory� of� the� DS2505� with� the� Extended� Read� Memory� command,� there� are� two�

�situations� where� a� 16-bit� CRC� is� transmitted.� One� 16-bit� CRC� follows� each� Redirection� Byte;� another�

�16-bit� CRC� is� received� after� the� last� byte� of� a� memory� data� page� is� read.� The� CRC� at� the� end� of� the�

�memory� page� is� always� the� result� of� clearing� the� CRC� generator� and� shifting� in� the� data� bytes� beginning�

�at� the� first� addressed� memory� location� of� the� EPROM� data� page� until� the� last� byte� of� this� page.� With� the�

�initial� pass� through� the� Extended� Read� Memory� flow� chart� the� 16-bit� CRC� value� is� the� result� of� shifting�

�the� command� byte� into� the� cleared� CRC� generator,� followed� by� the� 2� address� bytes� and� the� Redirection�

�Byte.� Subsequent� passes� through� the� Extended� Read� Memory� flow� chart� will� generate� a� 16-bit� CRC� that�

�is� the� result� of� clearing� the� CRC� generator� and� then� shifting� in� the� Redirection� Byte� only.�

�When� writing� to� the� DS2505� (either� data� memory� or� status� memory),� the� bus� master� receives� a� 16-bit�

�CRC� to� verify� the� correctness� of� the� data� transfer� before� applying� the� programming� pulse.� With� the�

�initial� pass� through� the� Write� Memory/Status� flow� chart� the� 16-bit� CRC� will� be� generated� by� clearing� the�

�CRC-generator,� shifting� in� the� command,� address� low,� address� high� and� the� data� byte.� Subsequent� passes�

�through� the� Write� Memory/Status� flow� chart� due� to� the� DS2505� automatically� incrementing� its� address�

�counter� will� generate� an� 16-bit� CRC� that� is� the� result� of� loading� (not� shifting)� the� new� (incremented)�

�address� into� the� CRC� generator� and� then� shifting� in� the� new� data� byte.�

�The� comparison� of� CRC� values� and� decision� to� continue� with� an� operation� are� determined� entirely� by� the�

�bus� master.� There� is� no� circuitry� on� the� DS2505� that� prevents� a� command� sequence� from� proceeding� if�

�the� CRC� stored� in� or� calculated� by� the� DS2505� does� not� match� the� value� generated� by� the� bus� master.�

�For� more� details� on� generating� CRC� values� including� example� implementations� in� both� hardware� and�

�software,� see� the� Book� of� DS19xx� iButton� Standards.�

�CRC-16� HARDWARE� DESCRIPTION� AND� POLYNOMIAL� Figure� 12�

�22� of� 24�

�相关PDF资料 |

PDF描述 |

|---|---|

| A42MX24-3PL84I | IC FPGA MX SGL CHIP 36K 84-PLCC |

| EP4CGX75DF27C8 | IC CYCLONE IV GX FPGA 75K 672FBG |

| A42MX24-2PQ208 | IC FPGA MX SGL CHIP 36K 208-PQFP |

| A42MX24-2PQG208 | IC FPGA MX SGL CHIP 36K 208-PQFP |

| EP4CE75F29C9LN | IC CYCLONE IV FPGA 75K 780FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2505P-UNW | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:UniqueWare Add-Only Memory |

| DS2505P-UNW-1154 | 制造商:Maxim Integrated Products 功能描述: |

| DS2505P-UNW-PPPP | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:UniqueWare Add-Only Memory |

| DS2505T | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:16-kbit Add-Only Memory |

| DS2505TR | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:16-kbit Add-Only Memory |

发布紧急采购,3分钟左右您将得到回复。