参数资料

| 型号: | DS26303DK |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 9/43页 |

| 文件大小: | 0K |

| 描述: | KIT DESIGN FOR DS26303 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 主要目的: | 电信,线路接口单元(LIU) |

| 已用 IC / 零件: | DS26303 |

| 已供物品: | 板,线缆,电源 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

�� �

�

�

�DS26303� Design� Kit�

�Telecom� Clock� and� Data� Test� Points�

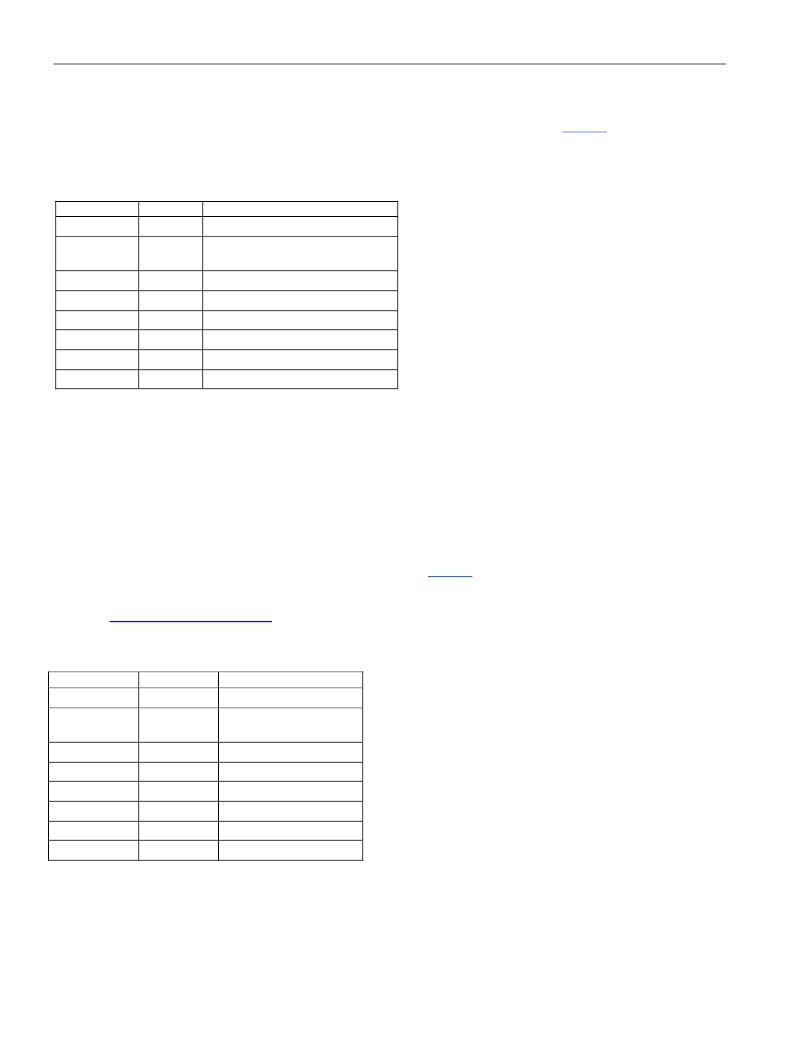

�The� DS26303DK� has� high-impedance� test� points� for� all� the� telecom� signals� that� are� related� to� the� LIU.� These�

�signals� are� split� up� by� port� number� and� marked� with� easy� to� read� silkscreen� labels.� Table 3� shows� the� telecom�

�connector� for� port� 1.� The� pinout� for� this� connector� is� repeated� for� all� 8� ports.�

�Table� 3.� Telecom� Connector� Pinout�

�PIN�

�1�

�2,� 4,� 6,� 8,�

�10,� 12,� 14�

�3�

�5�

�7�

�9�

�11�

�13�

�NAME�

�TCLK�

�GND�

�RCLK�

�TPOS�

�RPOS�

�TNEG�

�RNEG�

�RLOS�

�FUNCTION�

�Transmit� Clock� Input�

�Ground�

�Receive� Clock� Output�

�Transmit� Positive� Data� Input�

�Receive� Positive� Data� Output�

�Transmit� Negative� Data� Input�

�Receive� Positive� Data� Output�

�Receive� Loss-of-Signal� Output�

�Note� that� the� input� signals� in� the� telecom� connector� go� from� the� connector� to� the� on-board� FPGA,� then� to� the�

�DS26303.� The� FPGA� was� designed� to� perform� specific� signal� routing� functions� such� as� looping� back� RPOS� to�

�TPOS� on� a� particular� port� or� transferring� data� from� the� on-board� BERT.� If� you� are� using� user-defined� data� and�

�drive� the� signal� on� the� connector,� be� sure� to� tri-state� the� input� signal� in� the� FPGA.� FAILURE� TO� DO� SO� COULD�

�CAUSE� DAMAGE� TO� THE� FPGA� !�

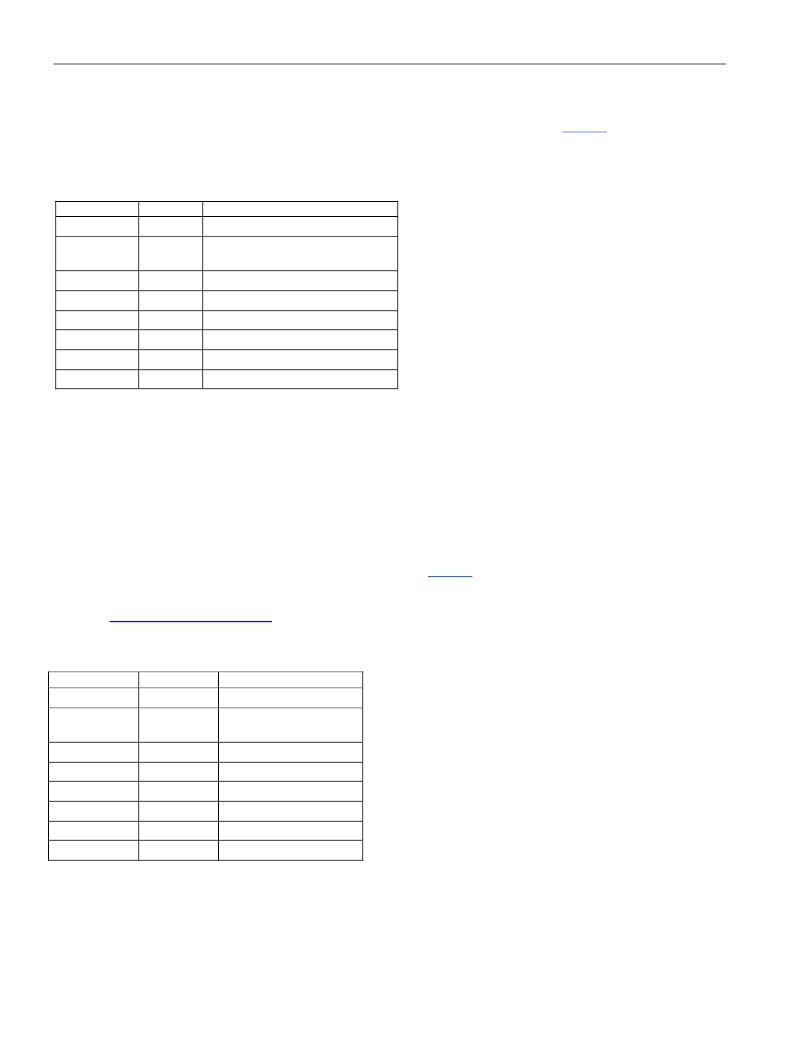

�On-Board� Bit� Error-Rate� Tester� (BERT)�

�The� DS26303DK� has� an� on-board� bit� error-rate� tester� (BERT)� to� generate� and� detect� errors� in� either�

�pseudorandom� or� user-defined� patterns.� The� BERT� on� the� DS26303DK� is� the� DS2174.� A� header� for� the� relevant�

�signals� related� to� the� BERT� is� located� on� the� board� (J17).� See� Table 4� for� the� pinout� of� the� BERT� connector.� The�

�BERT� signals� are� routed� into� the� FPGA� and� can� be� muxed� into� any� of� the� 8� DS26303� LIU� ports� under� software�

�control.� For� all� questions� concerning� the� operation� of� the� on-board� BERT,� refer� to� the� device� data� sheet� available�

�online� at� www.maxim-ic.com/telecom� .� If� you� are� using� user-defined� data� and� driver� the� signal� on� the� connector,� be�

�sure� to� tri-state� the� input� signal� in� the� FPGA.� FAILURE� TO� DO� SO� COULD� CAUSE� DAMAGE� TO� THE� FPGA!�

�Table� 4.� BERT� Connector� Pinout�

�PIN�

�1�

�2,� 4,� 6,� 8,�

�10,� 12,� 14�

�3�

�5�

�7�

�9�

�11�

�13�

�NAME�

�TCLK_EN�

�GND�

�TCLKIN�

�TCLKO�

�RCLKIN�

�RCLKEN�

�TDAT�

�RDAT�

�FUNCTION�

�BERT� TCLK� Enable�

�Ground�

�BERT� TCLK� Input�

�BERT� TCLK� Output�

�BERT� RCLK� Input�

�BERT� RCLK� Enable�

�BERT� TDAT� Output�

�BERT� RDAT� Input�

�9� of� 43�

�相关PDF资料 |

PDF描述 |

|---|---|

| DS26502DK | KIT DESIGN FOR DS26502 |

| DS26503DK | KIT DESIGN FOR DS26503 |

| DS26504DK | KIT DESIGN FOR DS26504 |

| DS26519DK | KIT DEMO FOR DS26519 |

| DS26521DK | KIT DESIGN FOR DS26521 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS26303G-120 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303G-75 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303GN-120 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303GN-75 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303L-120 | 功能描述:电信线路管理 IC 3.3V E1/T1/J1 Short Haul Octal LIU RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。