- 您现在的位置:买卖IC网 > PDF目录1915 > DS3154N+ (Maxim Integrated Products)IC LIU DS3/E3/STS-1 QD 144CSBGA PDF资料下载

参数资料

| 型号: | DS3154N+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/61页 |

| 文件大小: | 0K |

| 描述: | IC LIU DS3/E3/STS-1 QD 144CSBGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 160 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 4/4 |

| 规程: | IEEE 1149.1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA,CSPBGA |

| 供应商设备封装: | 144-TECSBGA(13x13) |

| 包装: | 管件 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

DS3151/DS3152/DS3153/DS3154 Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs

12 of 61

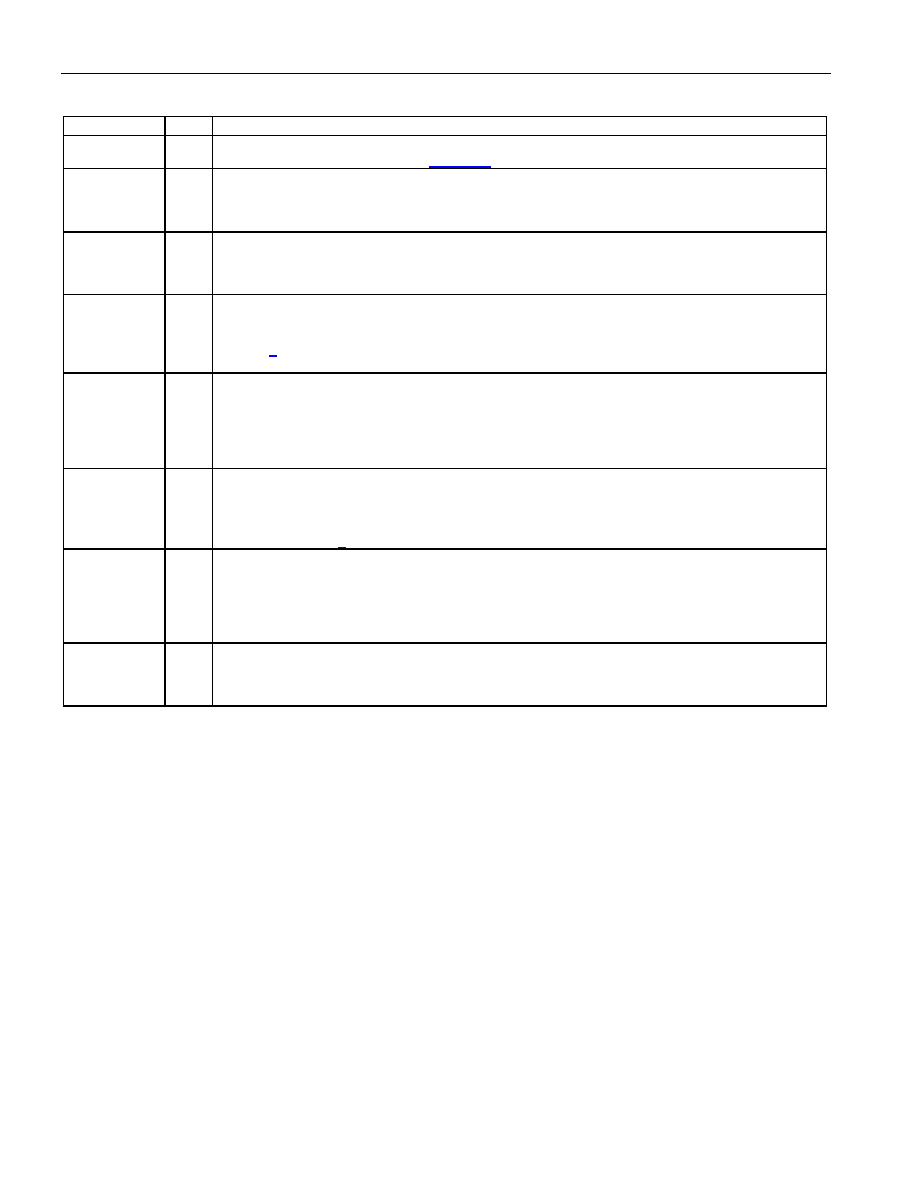

Table 4-C. Receiver Pin Descriptions

NAME

I/O

FUNCTION

RXPn,

RXNn

I

Receiver Analog Inputs. These differential AMI inputs are coupled to the inbound 75

Ω coaxial cable

through a 1:2 step-up transformer (Figure 1-1).

RCLKn

O3

Receiver Clock. The recovered clock is output on the RCLK pin. Recovered data is output on the

RPOS/RDAT and RNEG/RLCV pins on the falling edge of RCLK (RCINV = 0) or the rising edge of

RCLK (RCINV = 1). During a loss of signal (

RLOS = 0), the RCLK output signal is derived from the

LIU’s master clock.

RPOSn/

RDATn

O3

Receiver Positive AMI/Receiver Data. When the receiver is configured to have a bipolar interface

(RBIN = 0), RPOS pulses high for each positive AMI pulse received. When the receiver is

configured to have a binary interface (RBIN = 1), RDAT outputs decoded binary data. RPOS/RDAT

is updated either on the falling edge of RCLK (RCINV = 0) or the rising edge of RCLK (RCINV = 1).

RNEGn/

RLCVn

O3

Receiver Negative AMI/Line-Code Violation. When the receiver is configured to have a bipolar

interface (RBIN = 0), RNEG pulses high for each negative AMI pulse received. When the receiver is

configured to have a binary interface (RBIN = 1), RLCV pulses high to flag code violations. See

Section 6 for further details on code violations. RNEG/RLCV is updated either on the falling edge of

RCLK (RCINV = 0) or the rising edge of RCLK (RCINV = 1).

RTSn

I

Receiver Tri-State Enable (Active Low).

RTS tri-states the RPOS/RDAT, RNEG/RLCV, and RCLK

receiver outputs. This feature supports applications requiring LIU redundancy. Receiver outputs

from multiple LIUs can be wire-ORed together, eliminating the need for external switches or muxes.

The receiver continues to operate internally when

RTS is low.

0 = tri-state the receiver outputs

1 = enable the receiver outputs

RLOSn

O

Receiver Loss of Signal (Active Low, Open Drain).

RLOS is asserted upon detection of 175

±75

consecutive zeros in the receive data stream.

RLOS is deasserted when there are no excessive

zero occurrences over a span of 175

±75 clock periods. An excessive zero occurrence is defined as

three or more consecutive zeros in the DS3 and STS-1 modes or four or more zeros in the E3

mode. See Section 6 for additional details.

RMONn

I

Receive Monitor-Preamp Enable. RMON determines whether or not the receiver’s preamp is

enabled to provide flat gain to the incoming signal before the AGC/equalizer block processes it. This

feature should be enabled when the device is being used to monitor signals that have been

resistively attenuated by a monitor jack.

0 = disable the monitor preamp

1 = enable the monitor preamp

RJAn

I

Receiver Jitter Attenuator Enable

0 = remove jitter attenuator from the receiver path

1 = insert jitter attenuator into the receiver path

(Note that TJA = 1 takes precedence over RJA = 1.)

相关PDF资料 |

PDF描述 |

|---|---|

| DS3164+ | IC ATM/PACKET PHY QUAD 400-BGA |

| DS3170+ | IC TXRX DS3/E3 100-CSBGA |

| DS3172N+ | IC TXRX DS3/E3 DUAL 400-BGA |

| DS3181N+ | IC ATM/PACKET PHY W/LIU 400PBGA |

| DS32512N+ | IC LIU DS3/E3/STS-1 12P 484-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3154N# | 功能描述:网络控制器与处理器 IC Quad DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS3154N+ | 功能描述:网络控制器与处理器 IC Quad DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS3154NA2 | 功能描述:网络控制器与处理器 IC Quad DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS3154NB1 | 制造商:Maxim Integrated Products 功能描述:DS3154B QUAD DS3/E3 LIU IND - Rail/Tube 制造商:Maxim Integrated Products 功能描述:DS3/E3/STS-1 LIUS |

| DS3154NCA2 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

发布紧急采购,3分钟左右您将得到回复。