- 您现在的位置:买卖IC网 > PDF目录14304 > DS4510U-5+T&R (Maxim Integrated Products)IC SUPERVISOR W/NV MEM 10-USOP PDF资料下载

参数资料

| 型号: | DS4510U-5+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 6/12页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR W/NV MEM 10-USOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 3,000 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 可调节/可选择 |

| 电压 - 阀值: | 4.625V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-TFSOP,10-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 10-µMAX |

| 包装: | 带卷 (TR) |

�� �

�

�

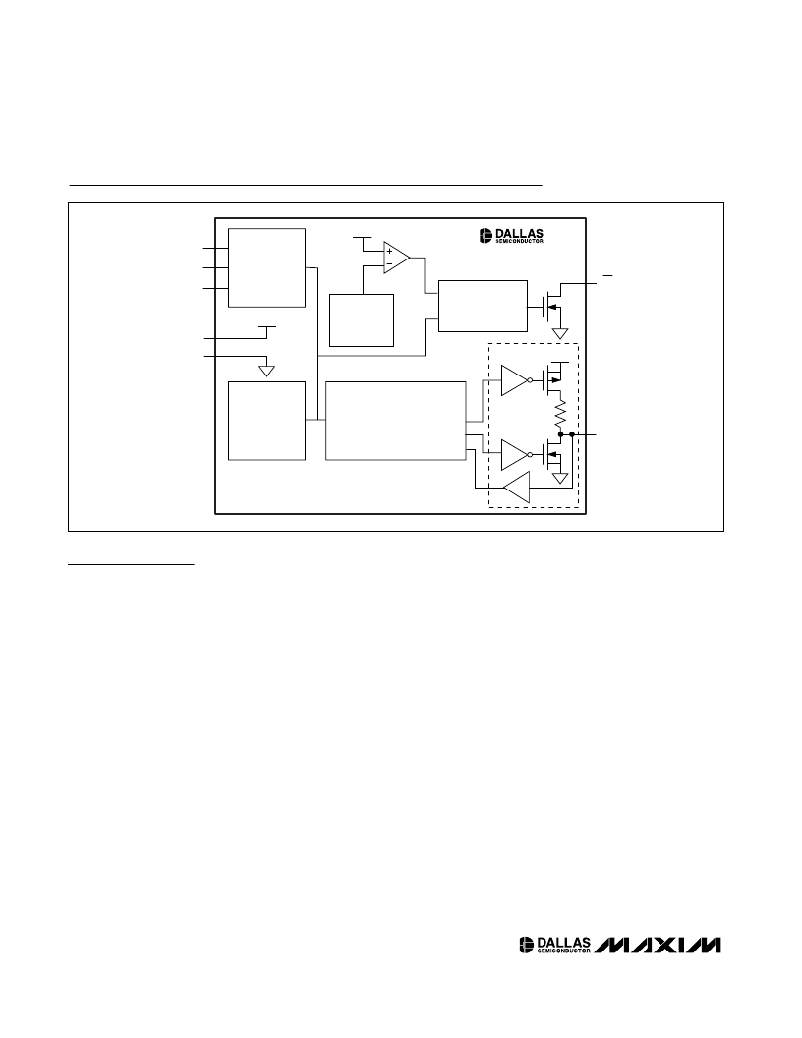

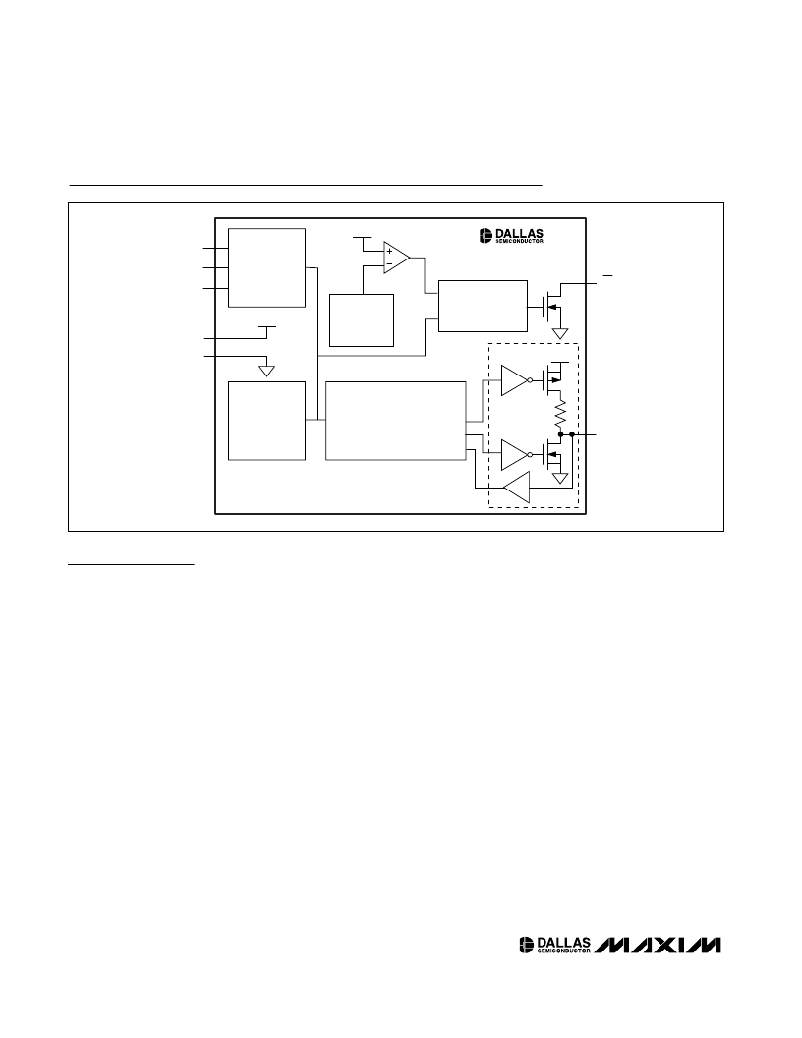

�CPU� Supervisor� with� Nonvolatile� Memory� and�

�Programmable� I/O�

�Functional� Diagram�

�V� CC�

�SDA�

�SCL�

�A0�

�2-WIRE�

�INTERFACE�

�DS4510�

�PROGRAMMABLE�

�RST�

�V� CC�

�V� CC�

�INTERNAL�

�VOLTAGE�

�REFERENCE�

�RESET�

�TIMER�

�GND�

�EEPROM�

�4� BIDIRECTIONAL�

�NONVOLATILE� I/O� LATCHES�

�4x�

�V� CC�

�64� BYTES�

�USER�

�MEMORY�

�PULLUP� ENABLE� (F0h)�

�I/O� X� CONTROL� (F4h-F7h)�

�R� P�

�4� NV�

�I/O� PINS�

�I/O� STATUS� (F8h)�

�Detailed� Description�

�The� DS4510� contains� a� CPU� supervisor,� four� program-�

�mable� I/O� pins,� and� a� 64-byte� EEPROM� memory.� All�

�functions� are� configurable� or� controllable� through� an�

�industry-standard� I� 2� C-compatible� bus.� DS4510� NV� reg-�

�isters� that� are� likely� to� require� frequent� modification� are�

�implemented� using� SRAM-shadowed� EEPROM� (SEEP-�

�ROM)� memory.� This� memory� is� configurable� to� act� as�

�volatile� SRAM� or� NV� EEPROM� by� adjusting� the� SEE� bit�

�in� the� Config� register.� Configuring� the� SEEPROM� as�

�SRAM� eliminates� the� EEPROM� write� time� and� allows�

�infinite� write� cycles� to� these� registers.� Configuring� the�

�registers� as� EEPROM� allows� the� application� to� change�

�the� power-on� values� that� are� recalled� during� power-up.�

�Programmable� CPU� Supervisor�

�The� timeout� period� is� adjusted� by� writing� the� reset�

�delay� register� (SEEPROM).� The� delay� for� each� setting�

�is� shown� in� the� CPU� Supervisor� AC� Electrical�

�Characteristics� .� If� the� SEE� bit� is� set,� changes� are� writ-�

�ten� to� SRAM.� On� power-up� the� last� value� written� to� the�

�EEPROM� is� recalled.� The� I� 2� C� bus� is� also� used� to� acti-�

�vate� the� RST� by� setting� the� SWRST� bit� in� the� Config�

�register.� This� bit� automatically� returns� to� zero� after� the�

�timeout� period.� The� Config� register� also� contains� the�

�ready� ,� trip� point,� and� reset� status� bits.� The� ready� bit�

�determines� if� the� power-on� reset� level� of� the� DS4510� is�

�surpassed� by� V� CC� .� The� trip� point� bit� determines� if� V� CC�

�is� above� V� CCTP� ,� and� the� reset� status� bit� is� set� if� RST� is�

�in� its� active� state.�

�Note� :� The� RST� pin� is� an� open-drain� output,� therefore� an�

�external� pullup� resistor� must� be� used� to� realize� high�

�logic� levels.�

�Programmable� NV� Digital� I/O� Pins�

�Each� programmable� I/O� X� pin� contains� an� input,� open-�

�collector� output,� and� a� selectable� internal� pullup� resis-�

�tor.� The� DS4510� stores� changes� to� the� I/O� X� pin� in�

�SEEPROM� memory.� Using� the� SEEPROM� as� SRAM� is�

�conducive� to� applications� such� as� I/O� expansion� that�

�generally� require� fast� access� times� and� frequent� modi-�

�fication� of� the� I/O� X� pin.� Configuring� the� SEEPROM� to�

�behave� as� EEPROM� allows� the� modification� of� the�

�power-on� state� of� the� I/O� X� pin.� During� power-up� the�

�I/O� X� pins� are� high� impedance� until� V� CC� exceeds� 2.0V�

�(typically),� which� is� when� the� last� value� programmed� is�

�recalled� from� EEPROM.� On� power-down,� the� I/O� X� state�

�is� maintained� until� V� CC� drops� below� 1.9V� (typically).�

�The� internal� pullups� for� each� I/O� X� pin� are� controlled� by�

�the� pullup-enable� register� (F0h).� Similarly,� the� individual�

�I/O� X� control� registers� (F4h� to� F7h)� adjust� the� pulldown�

�6�

�_____________________________________________________________________�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6401BS24+T | IC SUPERVISOR MPU 4-UCSP |

| MAX6401BS25+T | IC SUPERVISOR MPU 4-UCSP |

| MAX6401BS28+T | IC SUPERVISOR MPU 4-UCSP |

| MAX6401BS27+T | IC SUPERVISOR MPU 4-UCSP |

| MAX6401BS26+T | IC SUPERVISOR MPU 4-UCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS4514FP000 | 制造商:Thomas & Betts 功能描述:400A,CON,4P5W,MG,514,3PY347V |

| DS4514FP00K | 制造商:Thomas & Betts 功能描述:400AMP CON, 4P5W,MG,514,W/CONTACTS |

| DS4514FR000 | 制造商:Thomas & Betts 功能描述:400A,REC,4P5W,MG,514,3PY347V |

| DS4514FRAB0 | 制造商:Thomas & Betts 功能描述:400A,REC,4P5W,MG,514,3PY347V,AB0,SC |

| DS4514FRABK | 制造商:Thomas & Betts 功能描述:400A,REC,4P5W,MG,514,3P7347V,ABK,SC |

发布紧急采购,3分钟左右您将得到回复。