- 您现在的位置:买卖IC网 > PDF目录3831 > DSPIC33FJ128GP202-I/SP (Microchip Technology)IC DSPIC MCU/DSP 128K 28DIP PDF资料下载

参数资料

| 型号: | DSPIC33FJ128GP202-I/SP |

| 厂商: | Microchip Technology |

| 文件页数: | 59/73页 |

| 文件大小: | 0K |

| 描述: | IC DSPIC MCU/DSP 128K 28DIP |

| 特色产品: | PIC24FJ/33FJ MCUs & dsPIC? DSCs |

| 标准包装: | 15 |

| 系列: | dsPIC™ 33F |

| 核心处理器: | dsPIC |

| 芯体尺寸: | 16-位 |

| 速度: | 40 MIP |

| 连通性: | I²C,IrDA,LIN,SPI,UART/USART |

| 外围设备: | AC'97,欠压检测/复位,DMA,I²S,POR,PWM,WDT |

| 输入/输出数: | 21 |

| 程序存储器容量: | 128KB(128K x 8) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 8K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 3 V ~ 3.6 V |

| 数据转换器: | A/D 10x10b/12b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 28-DIP(0.300",7.62mm) |

| 包装: | 管件 |

| 产品目录页面: | 653 (CN2011-ZH PDF) |

| 配用: | MA330019-ND - PIM DSPIC33F MC 44P-100P QFN DV164033-ND - KIT START EXPLORER 16 MPLAB ICD2 DV164005-ND - KIT ICD2 SIMPLE SUIT W/USB CABLE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

DS70292G-page 62

2007-2012 Microchip Technology Inc.

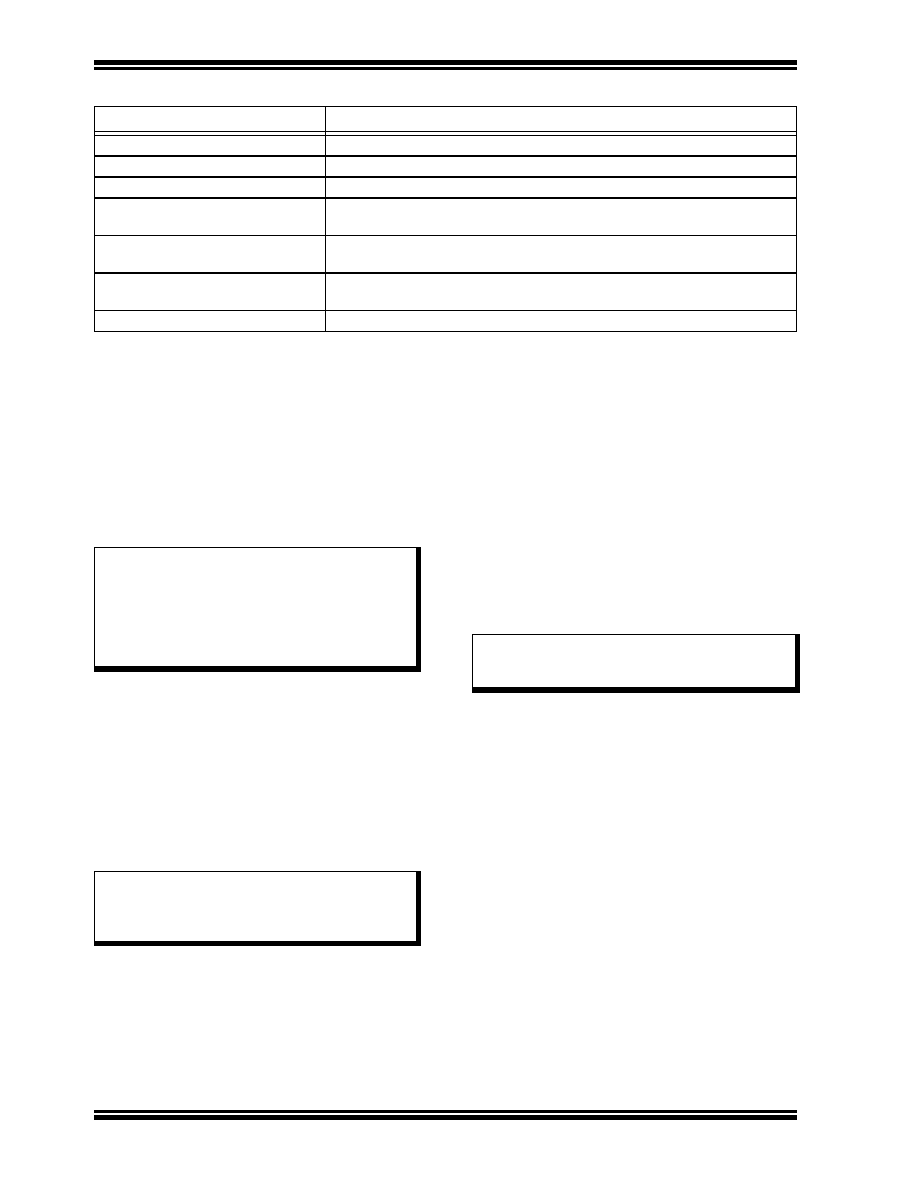

TABLE 4-37:

FUNDAMENTAL ADDRESSING MODES SUPPORTED

4.5.3

MOVE AND ACCUMULATOR

INSTRUCTIONS

Move instructions and the DSP accumulator class of

instructions provide a greater degree of addressing

flexibility than other instructions. In addition to the

addressing

modes

supported

by

most

MCU

instructions, move and accumulator instructions also

support Register Indirect with Register Offset

Addressing mode, also referred to as Register Indexed

mode.

In summary, the following addressing modes are

supported by move and accumulator instructions:

Register Direct

Register Indirect

Register Indirect Post-modified

Register Indirect Pre-modified

Register Indirect with Register Offset (Indexed)

Register Indirect with Literal Offset

8-bit Literal

16-bit Literal

4.5.4

MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED,

EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred

to as MAC instructions, use a simplified set of addressing

modes to allow the user application to effectively

manipulate the data pointers through register indirect

tables.

The two-source operand prefetch registers must be

members of the set {W8, W9, W10, W11}. For data

reads, W8 and W9 are always directed to the X RAGU,

and W10 and W11 are always directed to the Y AGU.

The effective addresses generated (before and after

modification) must, therefore, be valid addresses within

X data space for W8 and W9 and Y data space for W10

and W11.

In summary, the following addressing modes are

supported by the MAC class of instructions:

Register Indirect

Register Indirect Post-Modified by 2

Register Indirect Post-Modified by 4

Register Indirect Post-Modified by 6

Register Indirect with Register Offset (Indexed)

4.5.5

OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some

instructions use literal constants of various sizes. For

example, BRA (branch) instructions use 16-bit signed lit-

erals to specify the branch destination directly, whereas

the DISI instruction uses a 14-bit unsigned literal field. In

some instructions, such as ADD Acc, the source of an

operand or result is implied by the opcode itself. Certain

operations, such as NOP, do not have any operands.

Addressing Mode

Description

File Register Direct

The address of the file register is specified explicitly.

Register Direct

The contents of a register are accessed directly.

Register Indirect

The contents of Wn forms the Effective Address (EA).

Register Indirect Post-Modified

The contents of Wn forms the EA. Wn is post-modified (incremented

or decremented) by a constant value.

Register Indirect Pre-Modified

Wn is pre-modified (incremented or decremented) by a signed constant value

to form the EA.

Register Indirect with Register Offset

(Register Indexed)

The sum of Wn and Wb forms the EA.

Register Indirect with Literal Offset

The sum of Wn and a literal forms the EA.

Note:

For the MOV instructions, the addressing

mode specified in the instruction can differ

for the source and destination EA.

However, the 4-bit Wb (Register Offset)

field is shared by both source and

destination (but typically only used by

one).

Note:

Not all instructions support all the address-

ing modes given above. Individual instruc-

tions may support different subsets of

these addressing modes.

Note:

Register Indirect with Register Offset

Addressing mode is available only for W9

(in X space) and W11 (in Y space).

相关PDF资料 |

PDF描述 |

|---|---|

| PIC24FJ128GA310-I/BG | MCU 16BIT 128KB FLASH 121TFBGA |

| PIC24HJ128GP204-I/PT | IC PIC MCU FLASH 128K 44TQFP |

| PIC18F8393-I/PT | IC PIC MCU FLASH 4KX16 80TQFP |

| DSPIC33FJ128GP204-I/PT | IC DSPIC MCU/DSP 128K 44TQFP |

| DSPIC33FJ64MC802-I/MM | IC DSPIC MCU/DSP 64K 28-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| dsPIC33FJ128GP202T-I/MM | 功能描述:数字信号处理器和控制器 - DSP, DSC 16B DSC 28LD128KB DMA 40MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| dsPIC33FJ128GP202T-I/SO | 功能描述:数字信号处理器和控制器 - DSP, DSC 16B DSC 28LD128KB DMA 40MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| dsPIC33FJ128GP204-E/ML | 功能描述:数字信号处理器和控制器 - DSP, DSC 16b DSC 128KB Flash DMA 40MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| dsPIC33FJ128GP204-E/PT | 功能描述:数字信号处理器和控制器 - DSP, DSC 16b DSC 128KB Flash DMA 40MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| dsPIC33FJ128GP204-I/ML | 功能描述:数字信号处理器和控制器 - DSP, DSC 16B DSC 44LD128KB DMA 40MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。