- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC324-1 (ALTERA CORP) LOADABLE PLD, PBGA324 PDF资料下载

参数资料

| 型号: | EP20K100BC324-1 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA324 |

| 文件页数: | 8/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC324-1 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

16

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

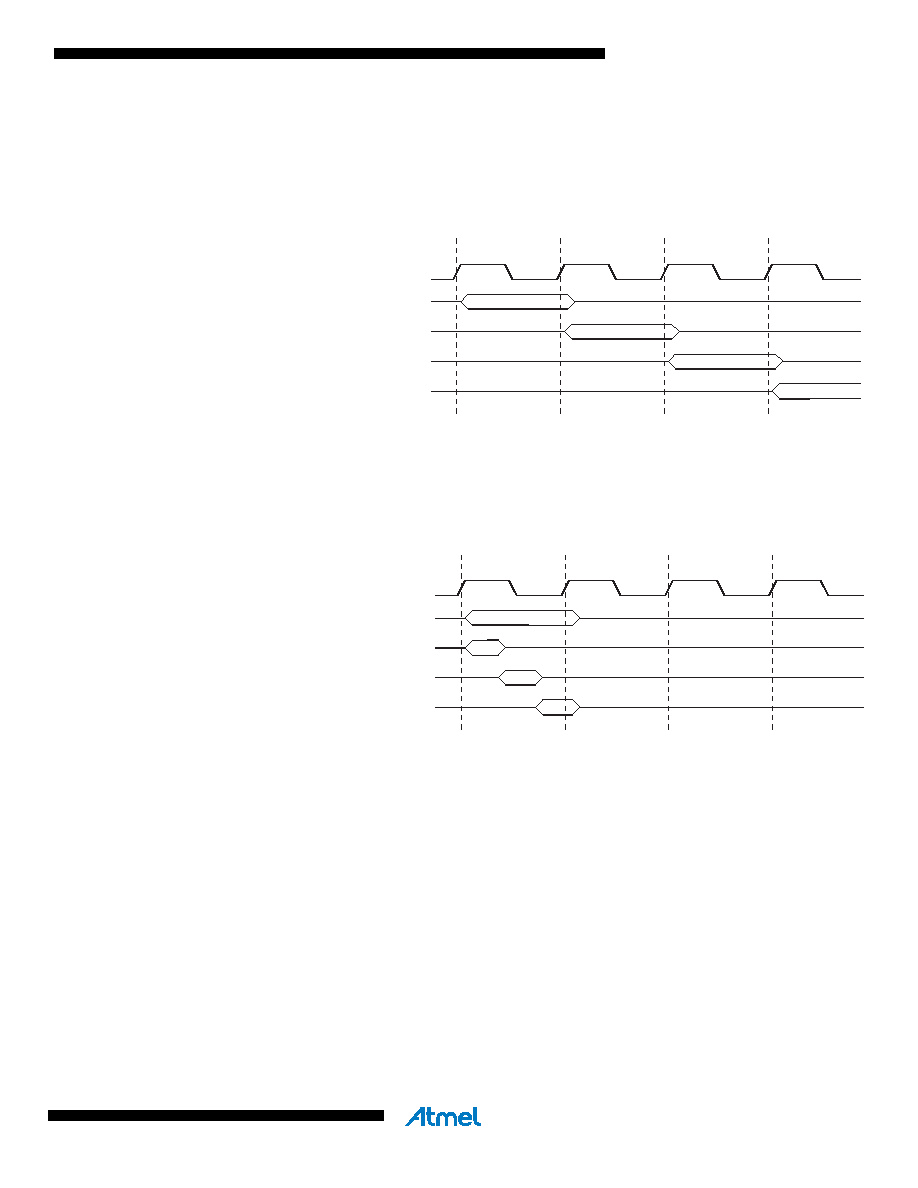

Figure 5-4 shows the parallel instruction fetches and instruction executions enabled by the Har-

vard architecture and the fast-access Register File concept. This is the basic pipelining concept

to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost,

functions per clocks, and functions per power-unit.

Figure 5-4.

The Parallel Instruction Fetches and Instruction Executions

Figure 5-5 shows the internal timing concept for the Register File. In a single clock cycle an ALU

operation using two register operands is executed, and the result is stored back to the destina-

tion register.

Figure 5-5.

Single Cycle ALU Operation

5.8

Reset and Interrupt Handling

The AVR provides several different interrupt sources. These interrupts and the separate Reset

Vector each have a separate program vector in the program memory space. All interrupts are

assigned individual enable bits which must be written logic one together with the Global Interrupt

Enable bit in the Status Register in order to enable the interrupt. Depending on the Program

Counter value, interrupts may be automatically disabled when Boot Lock bits BLB02 or BLB12

are programmed. This feature improves software security. See the section “Memory Program-

ming” on page 280 for details.

The lowest addresses in the program memory space are by default defined as the Reset and

Interrupt Vectors. The complete list of vectors is shown in “Interrupts” on page 57. The list also

determines the priority levels of the different interrupts. The lower the address the higher is the

priority level. RESET has the highest priority, and next is PSC2 CAPT – the PSC2 Capture

Event. The Interrupt Vectors can be moved to the start of the Boot Flash section by setting the

IVSEL bit in the MCU Control Register (MCUCR). Refer to “Interrupts” on page 57 for more infor-

mation. The Reset Vector can also be moved to the start of the Boot Flash section by

clk

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

T1

T2

T3

T4

CPU

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

T1

T2

T3

T4

clk

CPU

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC324-2 | LOADABLE PLD, PBGA324 |

| EP20K100BC324-3 | LOADABLE PLD, PBGA324 |

| EP20K100BI324-1 | LOADABLE PLD, PBGA324 |

| EP20K100BI324-2 | LOADABLE PLD, PBGA324 |

| EP20K100BI324-3 | LOADABLE PLD, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BC356-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BC356-1V | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP20K100BC356-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。