- 您现在的位置:买卖IC网 > PDF目录97915 > EP20K100ERC208-1ES Digitally Controlled Potentiometer (XDCP™) Terminal Voltage ±2.7V or ±5V, 128 Taps I2C Serial Interface; Temperature Range: -40°C to 85°C; Package: 10-MSOP PDF资料下载

参数资料

| 型号: | EP20K100ERC208-1ES |

| 元件分类: | 数字电位计 |

| 英文描述: | Digitally Controlled Potentiometer (XDCP™) Terminal Voltage ±2.7V or ±5V, 128 Taps I2C Serial Interface; Temperature Range: -40°C to 85°C; Package: 10-MSOP |

| 中文描述: | FPGA的 |

| 文件页数: | 104/114页 |

| 文件大小: | 1623K |

| 代理商: | EP20K100ERC208-1ES |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页当前第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页

Altera Corporation

9

APEX 20K Programmable Logic Device Family Data Sheet

Functional

Description

APEX 20K devices incorporate LUT-based logic, product-term-based

logic, and memory into one device. Signal interconnections within

APEX 20K devices (as well as to and from device pins) are provided by the

FastTrack Interconnect—a series of fast, continuous row and column

channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row

and column of the FastTrack Interconnect. Each IOE contains a

bidirectional I/O buffer and a register that can be used as either an input

or output register to feed input, output, or bidirectional signals. When

used with a dedicated clock pin, these registers provide exceptional

performance. IOEs provide a variety of features, such as 3.3-V, 64-bit,

66-MHz PCI compliance; JTAG BST support; slew-rate control; and

tri-state buffers. APEX 20KE devices offer enhanced I/O support,

including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL,

3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V

AGP I/O standards.

The ESB can implement a variety of memory functions, including CAM,

RAM, dual-port RAM, ROM, and FIFO functions. Embedding the

memory directly into the die improves performance and reduces die area

compared to distributed-RAM implementations. Moreover, the

abundance of cascadable ESBs ensures that the APEX 20K device can

implement multiple wide memory blocks for high-density designs. The

ESB’s high speed ensures it can implement small memory blocks without

any speed penalty. The abundance of ESBs ensures that designers can

create as many different-sized memory blocks as the system requires.

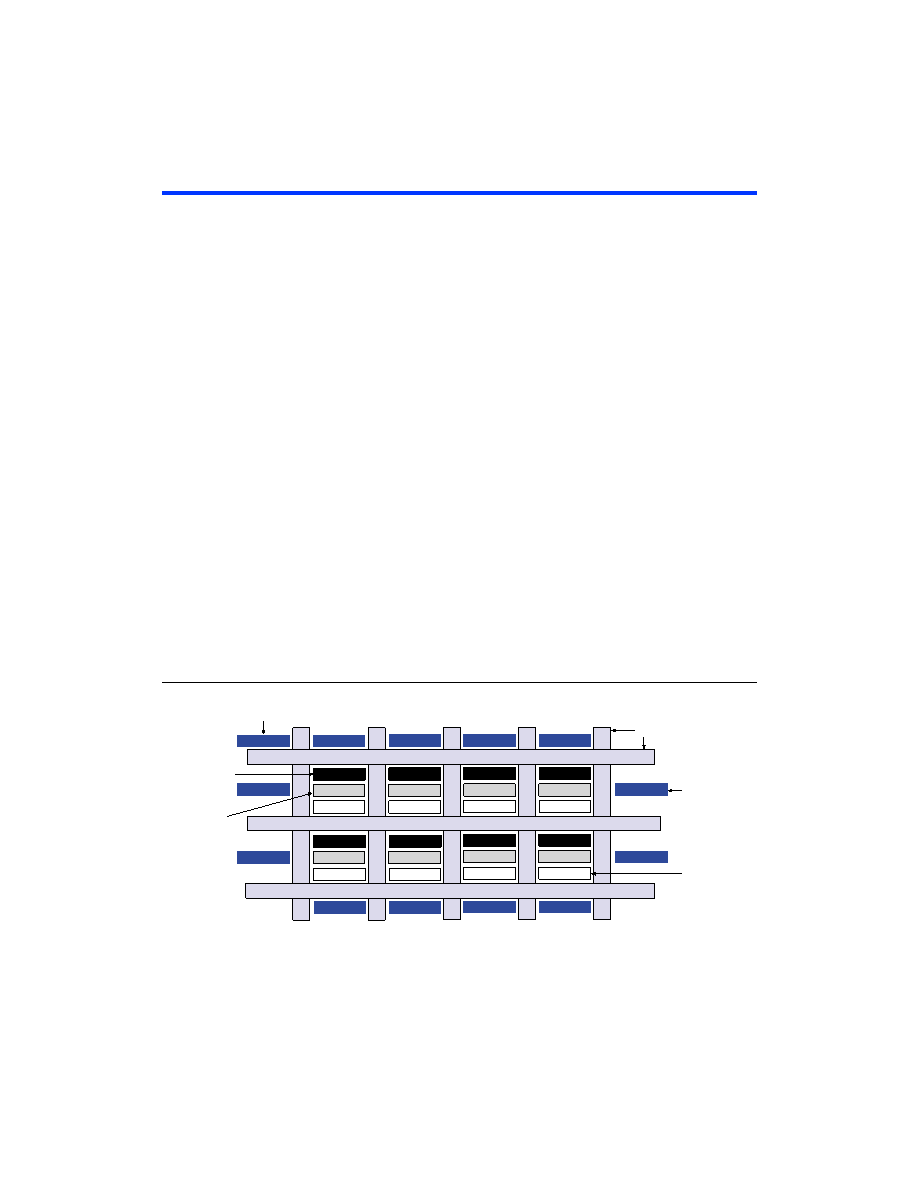

Figure 1 shows an overview of the APEX 20K device.

Figure 1. APEX 20K Device Block Diagram

LUT

Memory

IOE

LUT

Memory

IOE

Product Term

LUT

Memory

IOE

Product Term

FastTrack

Interconnect

Clock Management Circuitry

IOEs support

PCI, GTL+,

SSTL-3, LVDS,

and other

standards.

ClockLock

Four-input LUT

for data path and

DSP functions.

Product-term

integration for

high-speed

control logic and

state machines.

Flexible integration

of embedded

memory, including

CAM, RAM,

ROM, FIFO, and

other memory

functions.

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100ERC208-2ES | Digitally Controlled Potentiometer (XDCP™) Terminal Voltage ±2.7V or ±5V, 128 Taps I2C Serial Interface; Temperature Range: -40°C to 85°C; Package: 10-MSOP T&R |

| EP20K100ERC208-3ES | Single Digitally Controlled Potentiometer (XDCP™); Temperature Range: -40°C to 85°C; Package: 8-DFN |

| EP20K100ETI144-2ES | 600kHz/1.2MHz PWM Step-Up Regulator; Temperature Range: -40°C to 85°C; Package: 8-MSOP T&R |

| EP20K100ETI144-3ES | FPGA |

| EP20K100FC324-1 | Field Programmable Gate Array (FPGA) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100ERC208-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100ERC208-3ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100ERC240-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100ERC240-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100ERC240-3ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。