- 您现在的位置:买卖IC网 > PDF目录17075 > EVAL-AD5371EBZ (Analog Devices Inc)BOARD EVAL FOR AD5371 PDF资料下载

参数资料

| 型号: | EVAL-AD5371EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/29页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD5371 |

| 产品培训模块: | DAC Architectures |

| 标准包装: | 1 |

| DAC 的数量: | 40 |

| 位数: | 14 |

| 采样率(每秒): | 540k |

| 数据接口: | 串行 |

| 设置时间: | 20µs |

| DAC 型: | 电压 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板,CD |

| 已用 IC / 零件: | AD5371 |

| 相关产品: | AD5371BSTZ-REEL-ND - IC DAC 14BIT 40CH SER 80-LQFP AD5371BBCZ-REELTR-ND - IC DAC 14BIT 40CH SER 100-CSPBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD5371

Rev. B | Page 18 of 28

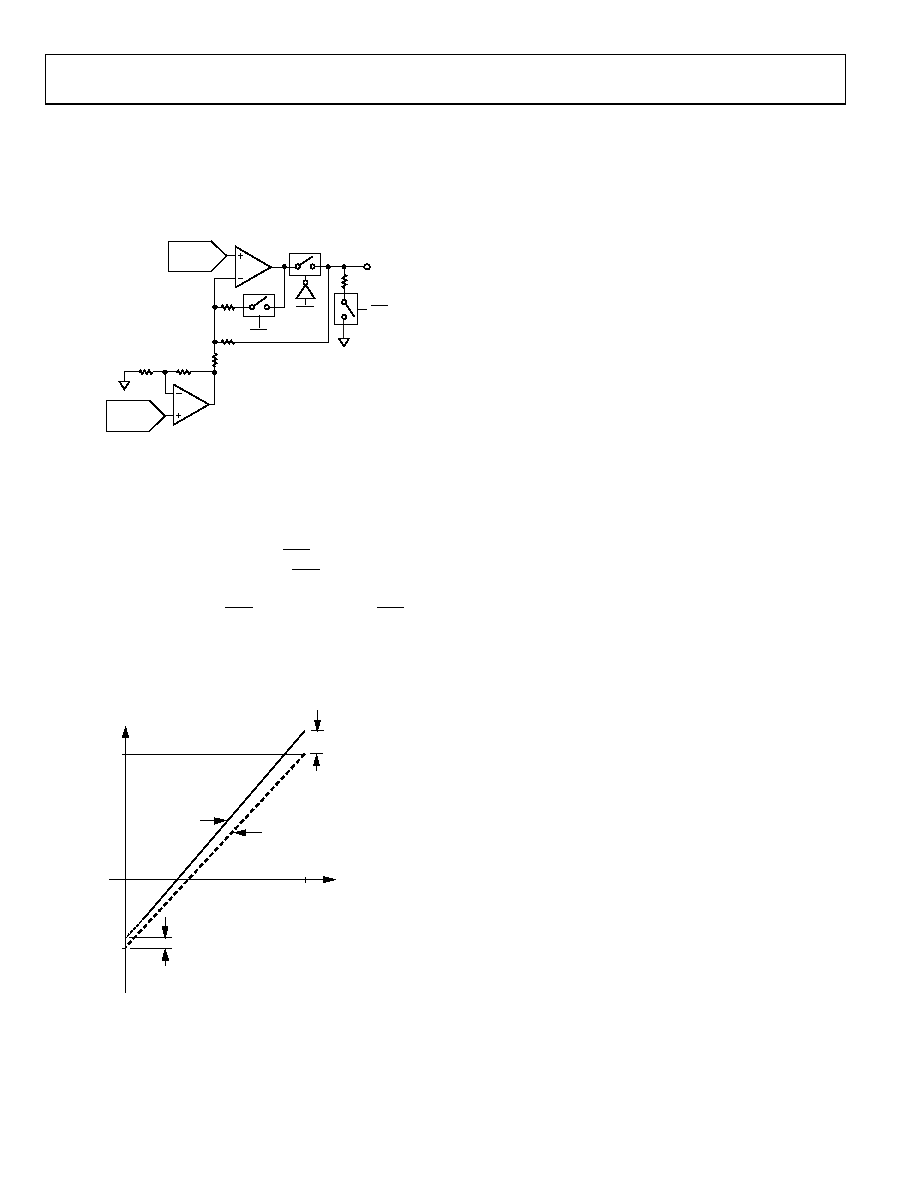

OUTPUT AMPLIFIER

The output amplifiers can swing to 1.4 V below the positive

supply and 1.4 V above the negative supply, which limits how

much the output can be offset for a given reference voltage. For

example, it is not possible to have a unipolar output range of

20 V, because the maximum supply voltage is ±16.5 V.

CLR

DAC

CHANNEL

OFFSET

DAC

VOUT

R6

10k

R2

20k

S3

S2

S1

R4

60k

R3

20k

SIGGNDx

R5

60k

R1

20k

05

81

4-

0

22

Figure 22. Output Amplifier and Offset DAC

Figure 22 shows details of a DAC output amplifier and its

connections to its corresponding offset DAC. On power-up,

S1 is open, disconnecting the amplifier from the output. S3 is

closed, so the output is pulled to the corresponding SIGGNDx

(R1 and R2 are greater than R6). S2 is also closed to prevent the

output amplifier from being open-loop. If CLR is low at power-up,

the output remains in this condition until CLR is taken high.

The DAC registers can be programmed, and the outputs assume

the programmed values when CLR is taken high. Even if CLR is

high at power-up, the output remains in this condition until

VDD > 6 V and VSS < 4 V and the initialization sequence has

finished. The outputs then go to their power-on default value.

TRANSFER FUNCTION

DAC CODE

FULL-SCALE

ERROR

+

ZERO-SCALE

ERROR

ZERO-SCALE

ERROR

–4V

0

16383

8V

IDEAL

TRANSFER

FUNCTION

ACTUAL

TRANSFER

FUNCTION

OUTPUT

VOLTAGE

05

81

4-

0

08

Figure 23. DAC Transfer Function

The output voltage of a DAC in the AD5371 is dependent on the

value in the input register, the value of the M and C registers,

and the value in the offset DAC.

The input code is the value in the X1A or X1B register that is

applied to the DAC (X1A, X1B default code = 5461).

DAC_CODE = INPUT_CODE × (M + 1)/214 + C 213.

where:

M = code in gain register default code = 214 1.

C = code in offset register default code = 213.

The DAC output voltage is calculated as follows:

VOUT = 4 × VREFx × (DAC_CODE –

OFFSET_CODE)/214 + VSIGGND

where:

DAC_CODE should be within the range of 0 to 16,383.

VREF = 3.0 V for a 12 V span and 5.0 V for a 20 V span.

OFFSET_CODE is the code loaded to the offset DAC. On

power-up, the default code loaded to the offset DAC is 5461

(0x1555). With a 3 V reference, this gives a span of 4 V to +8 V.

REFERENCE SELECTION

The AD5371 has three reference input pins. The voltage applied

to the reference pins determines the output voltage span on

VOUT0 to VOUT39. VREF0 determines the voltage span for

VOUT0 to VOUT7 (Group 0), VREF1 determines the voltage

span for VOUT8 to VOUT15 (Group 1), and VREF2 deter-

mines the voltage span for VOUT16 to VOUT39 (Group 2 to

Group 4). The reference voltage applied to each VREF pin can

be different, if required, allowing each group to have a different

voltage span. The output voltage range and span can be adjusted

further by programming the offset and gain registers for each

channel and by programming the offset DACs. If the offset and

gain features are not used (that is, the M and C registers are left

at their default values), the required reference levels can be

calculated as follows:

VREF = (VOUTMAX VOUTMIN)/4

If the offset and gain features of the AD5371 are used, the

required output range is slightly different. The selected output

range should take into account the system offset and gain errors

that need to be trimmed out. Therefore, the selected output

range should be larger than the actual required range.

Calculate the required reference levels as follows:

1.

Identify the nominal output range on VOUT.

2.

Identify the maximum offset span and the maximum gain

required on the full output signal range.

3.

Calculate the new maximum output range on VOUT,

including the expected maximum offset and gain errors.

4.

Choose the new required VOUTMAX and VOUTMIN, keeping

the VOUT limits centered on the nominal values. Note that

VDD and VSS must provide sufficient headroom.

5.

Calculate the value of VREF as follows:

VREF = (VOUTMAX VOUTMIN)/4

相关PDF资料 |

PDF描述 |

|---|---|

| EMC05DRTF-S13 | CONN EDGECARD 10POS .100 EXTEND |

| SC53LC-470 | INDUCTOR SMD 47UH 0.62A 100KHZ |

| V375C2E50BF | CONVERTER MOD DC/DC 2V 50W |

| 101-1102 | KIT DEV RABBIT RCM4100 INTL |

| RCC17DRXN | CONN EDGECARD 34POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5372EBZ | 功能描述:BOARD EVAL FOR AD5372 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5373EBZ | 功能描述:BOARD EVAL FOR AD5373 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5379EB | 制造商:AD 制造商全称:Analog Devices 功能描述:40-Channel, 14-Bit, Parallel and Serial Input, Bipolar Voltage-Output DAC |

| EVAL-AD5379EBZ | 功能描述:BOARD EVALUATION FOR AD5379 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5380EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。