- 您现在的位置:买卖IC网 > PDF目录16569 > EVAL-AD5930EBZ (Analog Devices Inc)BOARD EVAL FOR AD5930 PDF资料下载

参数资料

| 型号: | EVAL-AD5930EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD5930 |

| 标准包装: | 1 |

| 主要目的: | 计时,波形发生器 |

| 已用 IC / 零件: | AD5930 |

| 次要属性: | 串行接口 |

| 已供物品: | 板,线缆 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD5930

Data Sheet

Rev. B | Page 22 of 28

APPLICATIONS

GROUNDING AND LAYOUT

The printed circuit board that houses the AD5930 should be

designed so that the analog and digital sections are separated

and confined to certain areas of the board. This facilitates the

use of ground planes that can be easily separated. A minimum

etch technique is generally best for ground planes because it

gives the best shielding. Digital and analog ground planes

should only be joined in one place. If the AD5930 is the only

device requiring an AGND to DGND connection, then the

ground planes should be connected at the AGND and DGND

pins of the AD5930. If the AD5930 is in a system where

multiple devices require AGND to DGND connections, the

connection should be made at one point only, a star ground

point that should be established as close as possible to the

AD5930.

Avoid running digital lines under the device as these couple

noise onto the die. The analog ground plane should be allowed

to run under the AD5930 to avoid noise coupling. The power

supply lines to the AD5930 should use as large a track as

possible to provide low impedance paths and reduce the effects

of glitches on the power supply line. Fast switching signals, such

as clocks, should be shielded with digital ground to avoid

radiating noise to other sections of the board. Avoid crossover

of digital and analog signals. Traces on opposite sides of the

board should run at right angles to each other. This reduces the

effects of feedthrough through the board. A microstrip

technique is by far the best, but is not always possible with a

double-sided board. In this technique, the component side of

the board is dedicated to ground planes, while signals are placed

on the other side.

Good decoupling is important. The analog and digital supplies

to the AD5930 are independent and separately pinned out to

minimize coupling between analog and digital sections of the

device. All analog and digital supplies should be decoupled to

AGND and DGND, respectively, with 0.1 μF ceramic capacitors

in parallel with 10 μF tantalum capacitors. To achieve the best

from the decoupling capacitors, they should be placed as close

as possible to the device, ideally right up against the device. In

systems where a common supply is used to drive both the

AVDD and DVDD of the AD5930, it is recommended that the

system’s AVDD supply be used. This supply should have the

recommended analog supply decoupling between the AVDD

pins of the AD5930 and AGND, and the recommended digital

supply decoupling capacitors between the DVDD pins and

DGND.

Proper operation of the comparator requires good layout

strategy. The strategy must minimize the parasitic capacitance

between VIN and the SIGN BIT OUT pin by adding isolation

using a ground plane. For example, in a multilayered board, the

VIN signal could be connected to the top layer and the SIGN

BIT OUT connected to the bottom layer, so that isolation is

provided between the power and ground planes.

Interfacing to Microprocessors

The AD5930 has a standard serial interface that allows the part

to interface directly with several microprocessors. The device

uses an external serial clock to write the data/control

information into the device. The serial clock can have a

frequency of 40 MHz maximum. The serial clock can be

continuous, or it can idle high or low between write operations.

When data/control information is being written to the AD5930,

FSYNC is taken low and is held low while the 16 bits of data are

being written into the AD5930. The FSYNC signal frames the

16 bits of information being loaded into the AD5930.

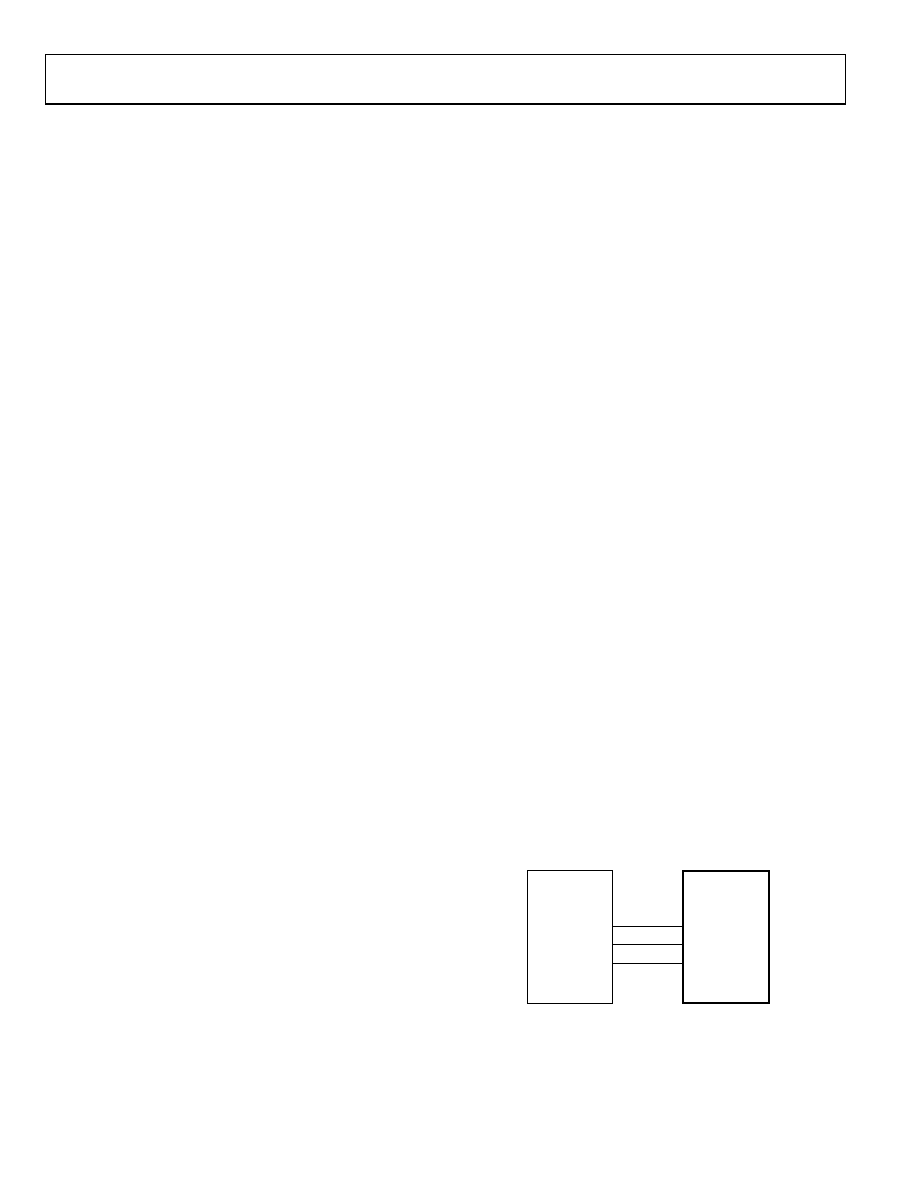

AD5930 TO ADSP-2101 INTERFACE

Figure 36 shows the serial interface between the AD5930 and

the ADSP-2101. The ADSP-2101 should be set up to operate in

the SPORT transmit alternate framing mode (TFSW = 1). The

ADSP-2101 is programmed through the SPORT control register

and should be configured as follows:

1.

Internal clock operation (ISCLK = 1)

2.

Active low framing (INVTFS = 1)

3.

16-bit word length (SLEN = 15)

4.

Internal frame sync signal (ITFS = 1)

5.

Generate a frame sync for each write (TFSR = 1)

Transmission is initiated by writing a word to the Tx register

after the SPORT has been enabled. The data is clocked out on

each rising edge of the serial clock and clocked into the AD5930

on the SCLK falling edge.

AD59301

ADSP-21011

1ADDITIONAL PINS OMITTED FOR CLARITY.

TFS

DT

SCLK

FSYNC

05

33

3-

0

38

SDATA

SCLK

Figure 36. ADSP-2101 to AD5930 Interface

相关PDF资料 |

PDF描述 |

|---|---|

| EBC31DCMI-S288 | CONN EDGECARD 62POS .100 EXTEND |

| A3DDB-1618G | IDC CABLE- AKR16B/AE16G/AKR16B |

| A1CXB-3436G | IDC CABLE- AKC34B/AE34G/X |

| GCM18DTBI | CONN EDGECARD 36POS R/A .156 SLD |

| H3CKH-1436G | IDC CABLE - HKC14H/AE14G/HPK14H |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5932EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD - Bulk |

| EVAL-AD5932EBZ | 功能描述:BOARD EVAL FOR AD5932 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVALAD5933EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Evaluation Board for the 1 MSPS 12-Bit Impedance Converter Network Analyzer |

| EVAL-AD5933EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-AD5933EB-U1 | 制造商:Analog Devices 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。