- 您现在的位置:买卖IC网 > PDF目录17060 > EVAL-AD7466CBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7466 PDF资料下载

参数资料

| 型号: | EVAL-AD7466CBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/29页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7466 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ 3.6 V |

| 在以下条件下的电源(标准): | 0.9mW @ 100kSPS,3 V |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7466 |

| 已供物品: | 板,CD |

| 相关产品: | AD7466BRTZREEL7DKR-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRTZ-R2-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRMZ-REEL7-ND - IC ADC 12BIT 1.6V LP 8-MSOP AD7466BRTZ-REEL-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRMZ-REEL-ND - IC ADC 12BIT 1.6V LP 8-MSOP AD7466BRTZREEL7CT-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRTZREEL7TR-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRMZ-ND - IC ADC 12BIT 1.6V LP 8-MSOP AD7466BRT-R2CT-ND - IC ADC 12BIT 1.6V LP SOT23-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD7466/AD7467/AD7468

Rev. C | Page 19 of 28

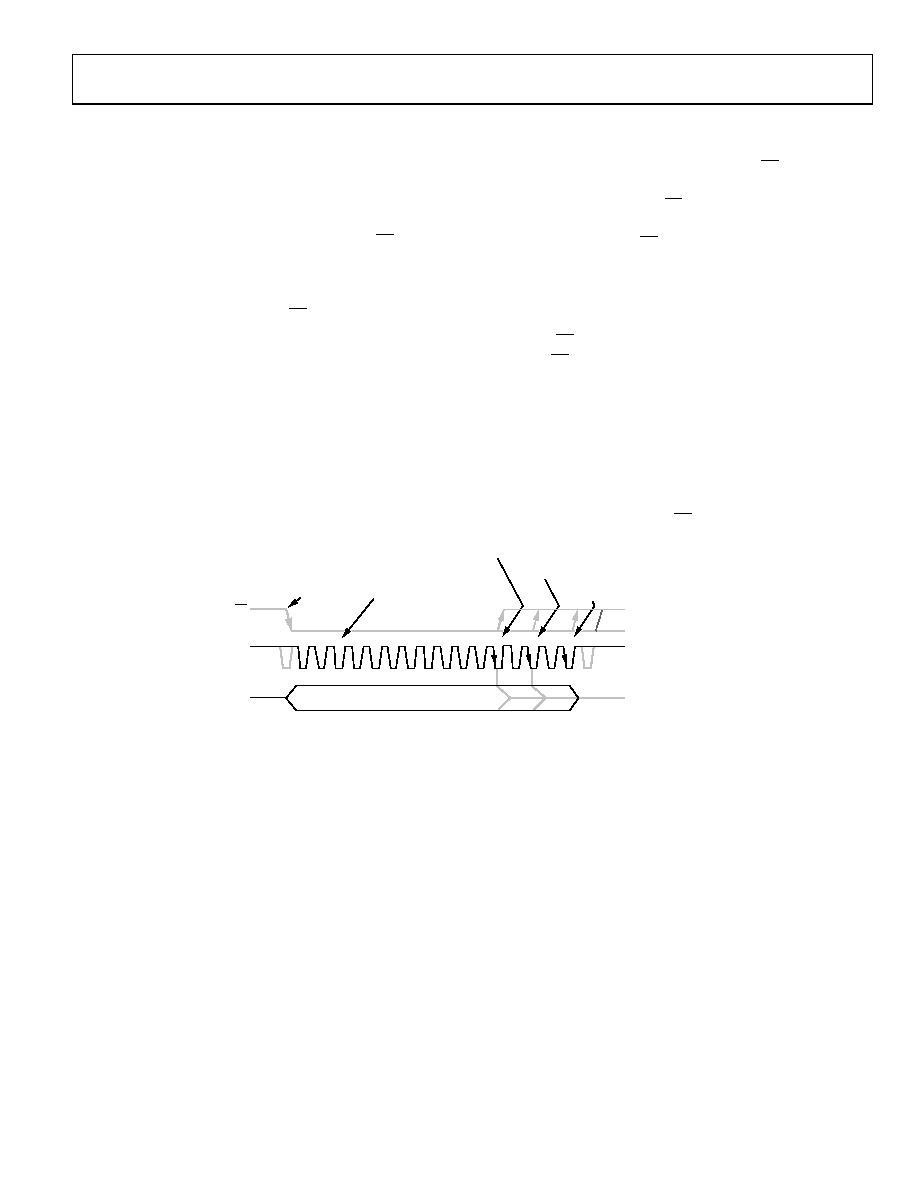

NORMAL MODE

The AD7466/AD7467/AD7468 automatically enter power-

down at the end of each conversion. This mode of operation is

designed to provide flexible power management options and to

optimize the power dissipation/throughput rate ratio for low

power application requirements. Figure 24 shows the general

operation of the AD7466/AD7467/AD7468. On the CS falling

edge, the part begins to power up and the track-and-hold,

which was in hold while the part was in power-down, goes into

track mode. The conversion is also initiated at this point. On

the third SCLK falling edge after the CS falling edge, the track-

and-hold returns to hold mode.

For the AD7466, 16 serial clock cycles are required to complete

the conversion and access the complete conversion result. The

AD7466 automatically enters power-down mode on the 16th

SCLK falling edge.

For the AD7467, 14 serial clock cycles are required to complete

the conversion and access the complete conversion result. The

AD7467 automatically enters power-down mode on the 14th

SCLK falling edge.

For the AD7468, 12 serial clock cycles are required to complete

the conversion and access the complete conversion result.

The AD7468 automatically enters power-down mode on the

12th SCLK falling edge.

The AD7466 also enters power-down mode if CS is brought

high any time before the 16th SCLK falling edge. The conver-

sion that was initiated by the CS falling edge terminates and

SDATA goes back into three-state. This also applies for the

AD7467 and AD7468; if CS is brought high before the conver-

sion is complete (the 14th SCLK falling edge for the AD7467,

and the 12th SCLK falling edge for the AD7468), the part enters

power-down, the conversion terminates, and SDATA goes back

into three-state.

Although CS can idle high or low between conversions,

bringing CS high once the conversion is complete is recom-

mended to save power.

When supplies are first applied to the devices, a dummy conver-

sion should be performed to ensure that the parts are in power-

down mode, the track-and-hold is in hold mode, and SDATA is

in three-state.

Once a data transfer is complete (SDATA has returned to three-

state), another conversion can be initiated after the quiet time,

tQUIET, has elapsed, by bringing CS low again.

THE PART BEGINS

TO POWER UP

AD7468 ENTERS POWER-DOWN

AD7467 ENTERS POWER-DOWN

AD7466 ENTERS POWER-DOWN

VALID DATA

SCLK

SDATA

12

3

12

14

16

THE PART IS POWERED UP

AND VIN FULLY ACQUIRED

CS

02643-025

Figure 24. Normal Mode Operation

相关PDF资料 |

PDF描述 |

|---|---|

| RCM15DCCD-S189 | CONN EDGECARD 30POS R/A .156 SLD |

| EVAL-AD7739EBZ | BOARD EVAL FOR AD7739 |

| EEV-HA1H330UP | CAP ALUM 33UF 50V 20% SMD |

| VE-B3B-EY | CONVERTER MOD DC/DC 95V 50W |

| EVAL-AD7738EBZ | BOARD EVAL FOR AD7738 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7467CB | 制造商:Analog Devices 功能描述:EVAL KIT FOR 1.6V, MICROPWR 12/10/8BIT ADCS - Bulk |

| EVAL-AD7470 | 制造商:AD 制造商全称:Analog Devices 功能描述:Evaluation Board for 10-/12-Bit High Speed, Low Power ADCs |

| EVAL-AD7470_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:Evaluation Board for 10-/12-Bit High Speed, Low Power ADCs |

| EVAL-AD7470CB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD7470 ADC - Bulk |

| EVAL-AD7470CB2 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.75 MSPS, 4 mW 10-Bit/12-Bit Parallel ADCs |

发布紧急采购,3分钟左右您将得到回复。