- 您现在的位置:买卖IC网 > PDF目录17060 > EVAL-AD7466CBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7466 PDF资料下载

参数资料

| 型号: | EVAL-AD7466CBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/29页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7466 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ 3.6 V |

| 在以下条件下的电源(标准): | 0.9mW @ 100kSPS,3 V |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7466 |

| 已供物品: | 板,CD |

| 相关产品: | AD7466BRTZREEL7DKR-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRTZ-R2-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRMZ-REEL7-ND - IC ADC 12BIT 1.6V LP 8-MSOP AD7466BRTZ-REEL-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRMZ-REEL-ND - IC ADC 12BIT 1.6V LP 8-MSOP AD7466BRTZREEL7CT-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRTZREEL7TR-ND - IC ADC 12BIT 1.6V LP SOT23-6 AD7466BRMZ-ND - IC ADC 12BIT 1.6V LP 8-MSOP AD7466BRT-R2CT-ND - IC ADC 12BIT 1.6V LP SOT23-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD7466/AD7467/AD7468

Rev. C | Page 21 of 28

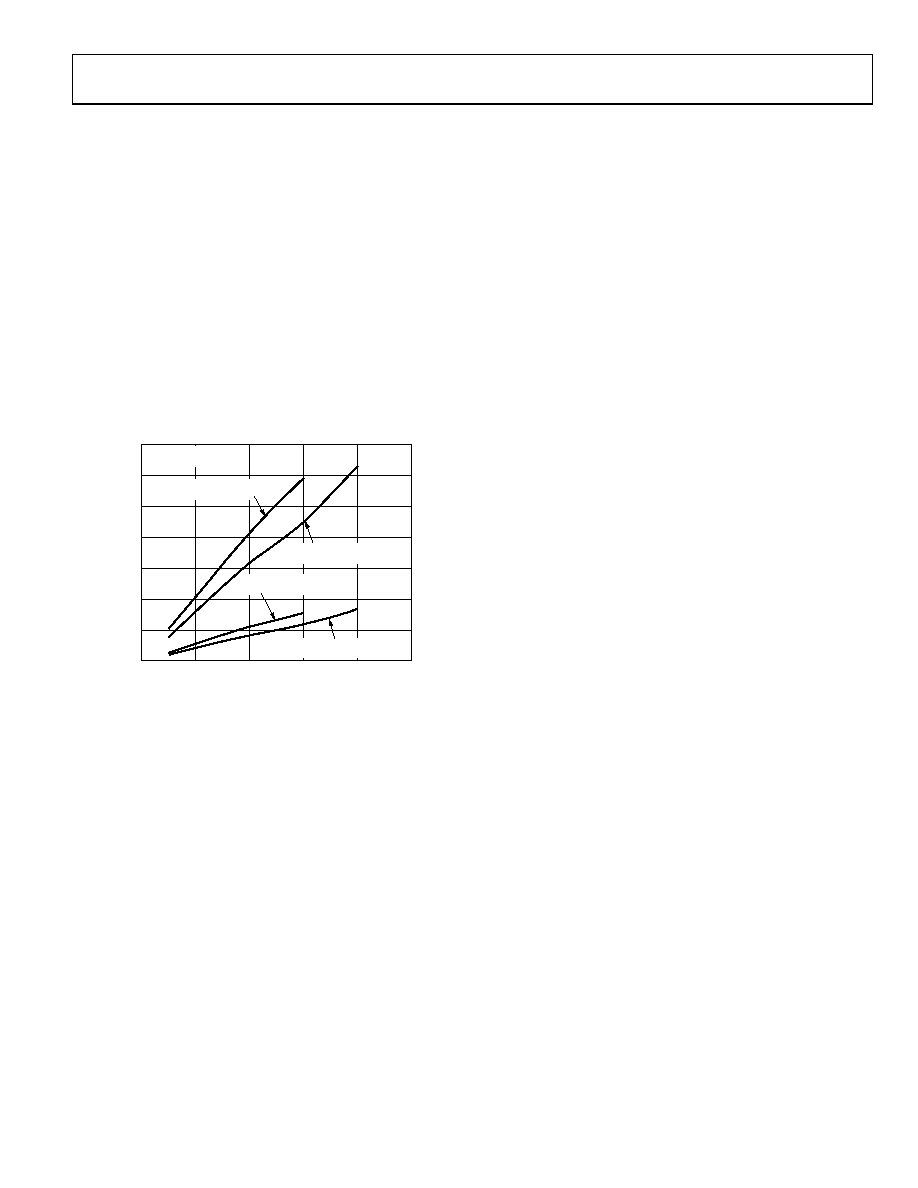

Figure 18 shows power consumption vs. throughput rate for a

3.4 MHz SCLK frequency. In this case, the conversion time is

the same for all cases because the SCLK frequency is a fixed

parameter. Low throughput rates lead to lower current con-

sumptions, with a higher percentage of the time in power-down

mode. Figure 27 shows two AD7466s running with the same

SCLK frequency, but at different throughput rates. The A

throughput rate is higher than the B throughput rate. The

slower the throughput rate, the longer the period of time the

part is in power-down mode, and the average power consump-

tion drops accordingly.

Figure 28 shows the power vs. throughput rate for different

supply voltages and SCLK frequencies. For this plot, all the

elements regarding power consumption that were explained

previously (the influence of the SCLK frequency, the influence

of the throughput rate, and the influence of the supply voltage)

are taken into consideration.

1.4

P

O

WE

R

(mW)

0.2

0.4

0.6

0.8

1.0

1.2

0

50

100

150

200

250

THROUGHPUT (kSPS)

TEMP = 25

°C

VDD = 3.0V, SCLK = 2.4MHz

VDD = 3.0V, SCLK = 3.4MHz

VDD = 1.8V, SCLK = 2.4MHz

VDD = 1.8V, SCLK = 3.4MHz

02643-029

Figure 28. Power vs. Throughput Rate

for Different SCLK and Supply Voltages

The following examples show calculations for the information

in this section.

Power Consumption Example 1

This example shows that, for a fixed throughput rate, as the

SCLK frequency increases, the average power consumption

drops. From Figure 26, for SCLK A = 3.4 MHz, SCLK B =

1.2 MHz, and a throughput rate of 50 kSPS, which gives a cycle

time of 20 μs, the following values can be obtained:

Conversion Time A = 16 × (1/SCLK A) = 4.7 μs

(23.5% of the cycle time)

Power-Down Time A = (1/Throughput) Conversion

Time A = 20 μs 4.7 μs = 15.3 μs (76.5% of the cycle time)

Conversion Time B = 16 × (1/SCLK B) = 13 μs

(65% of the cycle time)

Power-Down Time B = (1/Throughput) Conversion

Time B = 20 μs 13 μs = 7 μs (35% of the cycle time)

The average power consumption includes the power dissipated

when the part is converting and the power dissipated when the

part is in power-down mode. The average power dissipated

during conversion is calculated as the percentage of the cycle

time spent when converting, multiplied by the maximum

current during conversion. The average power dissipated in

power-down mode is calculated as the percentage of cycle time

spent in power-down mode, multiplied by the current figure for

power-down mode. In order to obtain the value for the average

power, these terms must be multiplied by the voltage.

Considering the maximum current for each SCLK frequency

for VDD = 1.8 V,

Power Consumption A = ((4.7/20) × 186 μA + (15.3/20) ×

100 nA) × 1.8 V = (43.71 + 0.076) μA × 1.8 V = 78.8 μW

= 0.07 mW

Power Consumption B = ((13/20) × 108 μA + (7/20) ×

100 nA) × 1.8 V = (70.2 + 0.035) μA × 1.8 V = 126.42 μW

= 0.126 mW

It can be concluded that for a fixed throughput rate, the average

power consumption drops as the SCLK frequency increases.

Power Consumption Example 2

This example shows that, for a fixed SCLK frequency, as the

throughput rate decreases, the average power consumption

drops. From Figure 27, for SCLK = 3.4 MHz, Throughput A =

100 kSPS (which gives a cycle time of 10 μs), and Throughput B

= 50 kSPS (which gives a cycle time of 20 μs), the following

values can be obtained:

Conversion Time A = 16 × (1/SCLK) = 4.7 μs

(47% of the cycle time for a throughput of 100 kSPS)

Power-Down Time A = (1/Throughput A) Conversion

Time A = 10 μs 4.7 μs = 5.3 μs (53% of the cycle time)

Conversion Time B = 16 × (1/SCLK) = 4.7 μs

(23.5% of the cycle time for a throughput of 50 kSPS)

Power-Down Time B = (1/Throughput B) Conversion

Time B = 20 μs 4.7 μs = 15.3 μs (76.5% of the cycle time)

The average power consumption is calculated as explained in

Power Consumption Example 1, considering the maximum

current for a 3.4 MHz SCLK frequency for VDD = 1.8 V.

Power Consumption A = ((4.7/10) × 186 μA + (5.3/10) ×

100 nA) × 1.8 V= (87.42 + 0.053) μA × 1.8 V = 157.4 μW =

0.157 mW

Power Consumption B = ((4.7/20) × 186 μA + (15.3/20) ×

100 nA) × 1.8 V = (43.7 + 0.076) μA × 1.8 V = 78.79 μW =

0.078 mW

It can be concluded that for a fixed SCLK frequency, the average

power consumption drops as the throughput rate decreases.

相关PDF资料 |

PDF描述 |

|---|---|

| RCM15DCCD-S189 | CONN EDGECARD 30POS R/A .156 SLD |

| EVAL-AD7739EBZ | BOARD EVAL FOR AD7739 |

| EEV-HA1H330UP | CAP ALUM 33UF 50V 20% SMD |

| VE-B3B-EY | CONVERTER MOD DC/DC 95V 50W |

| EVAL-AD7738EBZ | BOARD EVAL FOR AD7738 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7467CB | 制造商:Analog Devices 功能描述:EVAL KIT FOR 1.6V, MICROPWR 12/10/8BIT ADCS - Bulk |

| EVAL-AD7470 | 制造商:AD 制造商全称:Analog Devices 功能描述:Evaluation Board for 10-/12-Bit High Speed, Low Power ADCs |

| EVAL-AD7470_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:Evaluation Board for 10-/12-Bit High Speed, Low Power ADCs |

| EVAL-AD7470CB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD7470 ADC - Bulk |

| EVAL-AD7470CB2 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.75 MSPS, 4 mW 10-Bit/12-Bit Parallel ADCs |

发布紧急采购,3分钟左右您将得到回复。