- 您现在的位置:买卖IC网 > PDF目录17030 > EVAL-AD974CB (Analog Devices Inc)BOARD EVAL FOR AD974 PDF资料下载

参数资料

| 型号: | EVAL-AD974CB |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/20页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD974 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 输入范围: | ±10 V |

| 在以下条件下的电源(标准): | 120mW @ 200kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD974 |

| 已供物品: | 板 |

| 相关产品: | AD974BRZ-ND - IC DAS 16BIT 4CH 200KSPS 28SOIC AD974BNZ-ND - IC DAS 16BIT 4CH 200KSPS 28DIP AD974ARZ-ND - IC DAS 16BIT 4CH 200KSPS 28-SOIC AD974ARSZ-ND - IC DAS 16BIT 4CH 200KSPS 28-SSOP AD974ANZ-ND - IC DAS 16BIT 4CH 200KSPS 28DIP AD974BRS-RL7-ND - IC DAS 16BIT 4CH 200KSPS 28SSOP AD974BRSZ-ND - IC DAS 16BIT 4CH 200KSPS 28-SSOP AD974BRS-ND - IC DAS 16BIT 4CH 200KSPS 28-SSOP AD974BR-ND - IC DAS 16BIT 4CH 200KSPS 28-SOIC AD974BN-ND - IC DAS 16BIT 4CH 200KSPS 28-DIP 更多... |

REV. A

AD974

–10–

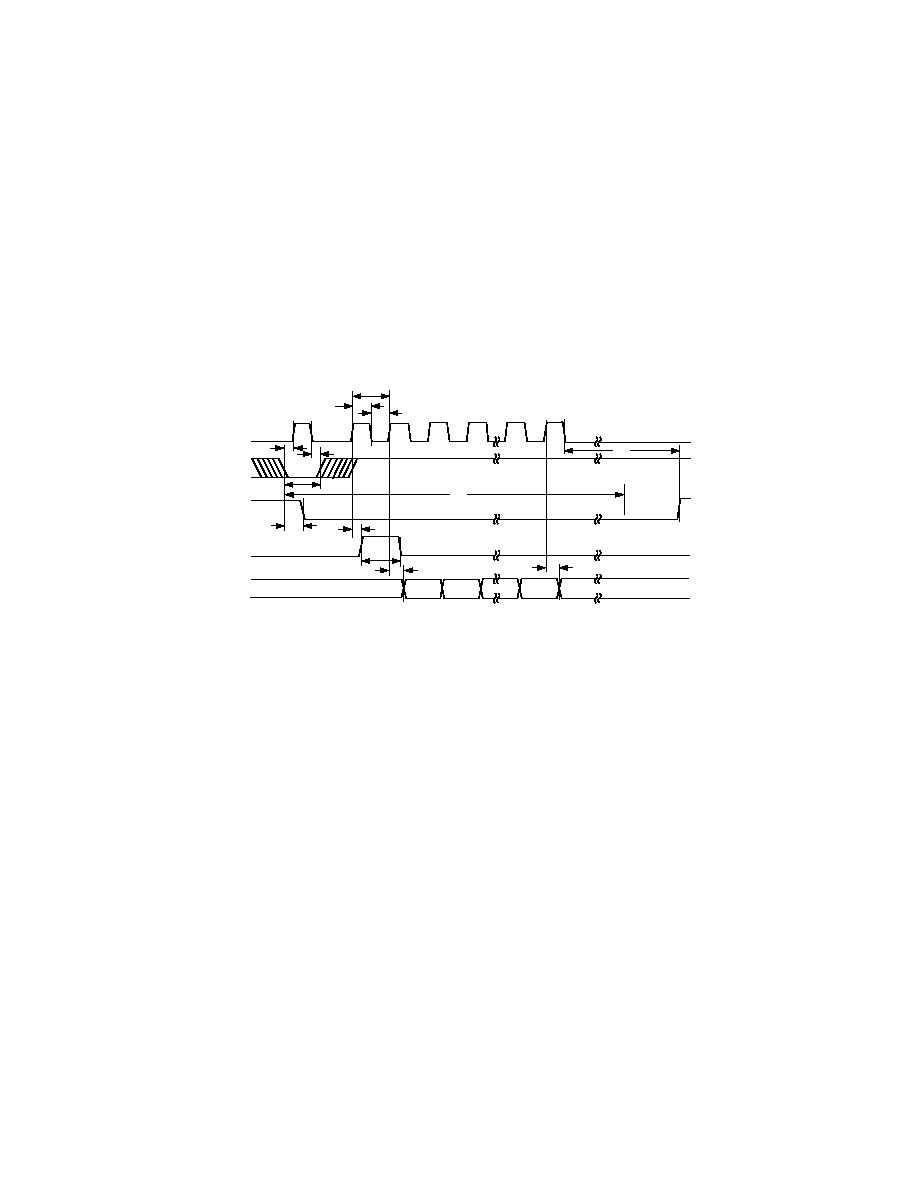

EXTERNAL DISCONTINUOUS CLOCK DATA READ

DURING CONVERSION WITH SYNC OUTPUT

GENERATED

Figure 7 illustrates the method by which data from conversion

“n-1” can be read during conversion “n” while using a discon-

tinuous external clock, with the generation of a SYNC output.

What permits the generation of a SYNC output is a transition of

DATACLK while either

CS is High or while both CS and R/C

are low. In Figure 7 a conversion is initiated by taking R/

C low

with

CS tied low. While this condition exists a transition of

DATACLK, clock pulse #0, will enable the generation of a

SYNC pulse. Less then 83 ns after R/

C is taken low the BUSY

output will go low to indicate that the conversion process has

begun. Figure 7 shows R/

C then going high and after a delay of

greater than 15 ns (t15) clock pulse #1 can be taken high to

request the SYNC output. The SYNC output will appear ap-

proximately 40 ns after this rising edge and will be valid on the

falling edge of clock pulse #1 and the rising edge of clock pulse

#2. The MSB will be valid approximately 40 ns after the rising

edge of clock pulse #2 and can be latched off either the falling

edge of clock pulse #2 or the rising edge of clock pulse #3. The

LSB will be valid on the falling edge of clock pulse #17 and the

rising edge of clock pulse #18.

Data should be clocked out during the first half of

BUSY to

avoid degrading conversion performance. This requires use of a

10 MHz DATACLK or greater, with data being read out as

soon as the conversion process begins.

t12

EXT

DATACLK

R/

C

BUSY

SYNC

DATA

0

t13

t14

t15

t22

t20

t1

t2

t17

t12

t18

BIT 15

(MSB)

BIT 14

BIT 0

(LSB)

1234

17

18

Figure 7. Conversion and Read Timing for Reading Previous Conversion Results During a Conversion

Using External Discontinuous Data Clock (EXT/

INT Set to Logic High, CS Set to Logic Low)

相关PDF资料 |

PDF描述 |

|---|---|

| GBM25DCTI | CONN EDGECARD 50POS DIP .156 SLD |

| GCC12DREH-S93 | CONN EDGECARD 24POS .100 EYELET |

| PI5PD2065TAEX | IC POWER DIST USB 2.3A 5SOT23 |

| EYM12DTMS-S189 | CONN EDGECARD 24POS R/A .156 SLD |

| PI5PD2065WEX | IC POWER DIST USB 2.3A 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD976ACB | 功能描述:BOARD EVAL FOR AD976A RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD976CB | 功能描述:BOARD EVAL FOR AD976 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD977ACB | 功能描述:BOARD EVAL FOR AD977A RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD977CB | 功能描述:BOARD EVAL FOR AD977 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD9830EBZ | 功能描述:BOARD EVALUATION AD9830 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。